FPGA引脚输出电平设置为3.3V,为什么输出才1V左右,我用的是EP3C25E144I7

时间:10-02

整理:3721RD

点击:

FPGA引脚输出电平设置为3.3V,为什么输出才1V左右,我用的是EP3C25E144I7

后级是否过载 晒图看看

后面直接连接的是单片机,现在问题是其他管脚输出都正常,都是3.3V左右,只有个别几个管脚输出是1V左右,我设置输出电平形式位3.3LVTTL

检查前后引脚配置吧

所有的引脚配置都一样,如果设置成默认的2.5V,输出电平就为正常的2.5V,不知道是什么原因。

求大神解答,现在这个问题还是一直没有解决。

自己检查管脚连接配置是否正确~!

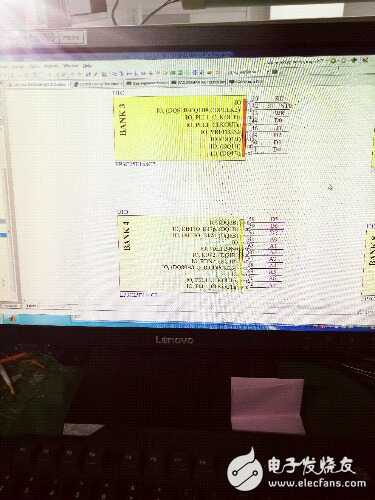

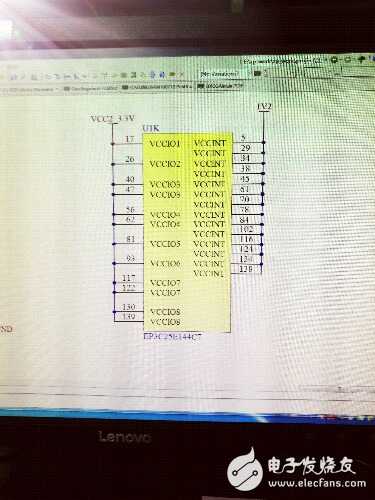

这是我的原理图,大神们帮忙看下

刚才图片没拍清楚,不好意思

你的问题解决了吗?我现在面临同样的问题,我用的是EP4CE6E22C8,你能留下你的联系方式吗,交流一下。

是不是负载把它拉低了

输出电流不足吧,3.3V最大8mA驱动能力,2.5/V最大可达16mA,记不太清楚了哈

你可以确定一下你的FPGA该引脚所在bank 的外部电压,是否是提供的bank电压不够。再确定设置的管脚电压是否是3.3V TTL