FPGA verilog жаЕїгУЕФtask ЕФЮЪЬт

[source lang="verilog"]

module process (clk,rst,ad,out);

input clk,rst;

input [15:0] ad;

output [15:0] out;

reg [15:0] memory_3,memory_2,memory_1;

reg clock,clkout;

reg [12:0] ii,jj,kk;

reg [15:0] adc_rms ;

wire remainder;

wire [15:0] RMS_adc_sqr;

wire [15:0] ad,data;

reg [2:0] stat;

reg [13:0] count;

reg [31:0] rms_adc_s2,rms_adc_s;

reg [15:0] RMS_adc;

reg wren;

reg [7:0] address;

parameter idle =3'b001,

start=3'b010,

ram =3'b011,

fsh =3'b100,

work =3'b101;

always@(negedge rst or posedge clk)

begin

if(ЃЁrst)

begin

count 4999 &&count memory_1 && memory_2>memory_3)

begin

address=0;

wren=1;

ram2(clk,wren,address,memory_1,adc_rms);

stat memory_1 &&memory_2>memory_3&&ii>4)

begin

jj =256)

begin

address=0;

wren=0;

rms_adc_s=ram2(clk,wren,address,ad,adc_rms);

rms_adc_s2 =jj)

begin

RMS_adc<=rms_adc_s2/(jj+1);

stat<=idle;

ii<=1;

kk<=0;

jj<=0;

rms_adc_s2<=0;

end

defaultstat<=idle;

endcase

end

end

assign out = RMS_adc;

task ram2;

input clk,wren,address,data;

output adc_rms;

begin

ram ram1( .address (address),

.q (adc_rms),

.clock (clk),

.wren (wren),

.data (data)

);

end

endtask

endmodule

[/source]

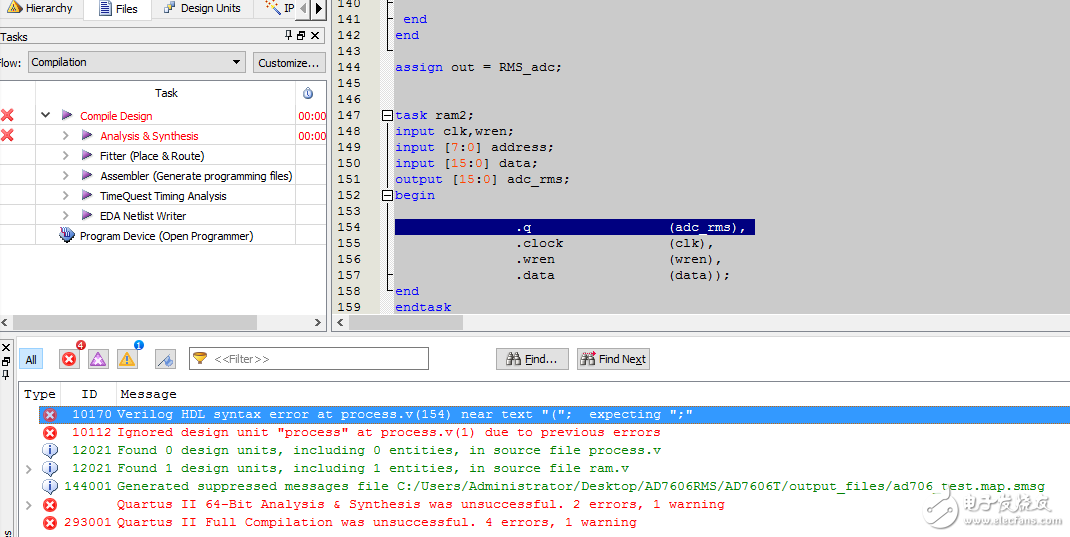

ram ЪЧЮвЕїгУЕФвЛИіIP RAM-1PORTЃЌвђЮЊВЛФмдкcaseРяУцЕїгУЃЌОЭАбЫћЗХдкСЫtask жаЃЌШЛКѓдйtaskРяУцЕїгУЫћЃЌВЛжЊЕРетбљаДПЩвдВЛЃЌБОШЫГѕбЇЃЌаЛаЛИїЮЛСЫ

1ЁЂtaskШчЙћЪЧзщКЯТпМЕФЛАЃЌЪЧПЩвдзлКЯЕФ

2ЁЂЕїгУIPЃЌжБНгР§ЛЏОЭПЩвдЃЌВЛФмдкtaskЛђепalwaysФЃПщжаЕїгУ

здЖЅЁЃ

taskВЛФмзлКЯЃЌжЛФмдкtestbenchРяБпгУЃЌЛђепЫЕгызлКЯШэМўгаЙиЃЌгааЉШэМўВЛФмзлКЯЃЌВЛНЈвщЪЙгУtask

аЛаЛ2ЮЛЕФЛиД№ЃЌжБНгР§ЛЏКѓОЭКУСЫЃЌЕЋЪЧгаИівЩЮЪЃЌФЧtask КЭfunction ЩЖЪБКђгУФи?

етСНИідкЪЕМЪЙЄГЬЯюФПРяКмЩйгУЕНЃЌвЛАуЗТецЪБгУдкtestbenchРя

ЖїЃЌtwzЫЕЕФЪЧЖдЕФЃЌtaskвЛАуЪЧгУдкtbжаЕФЃЌвЛАуmoduleВЛгУtaskЃЌfunctionетаЉЕФЁЃ

ЖїЖїЃЌаЛаЛЃЌКУЕФ

ЛсгУtaskЃЌаДtestbenchЕФЪБКђЃЌЗТецИїжжзмЯпМђжБ6ЕФЗЩЦ№ЃЌЮвдРДВЛЛсгУtaskЃЌФЃФтЪБађЕФЪБКђвЛИізжНкЕФМЄРјвЊаДnЖрОфЛАЃЌгУСЫtaskЃЌвЛОфЛАИуЖЈ