时序约束后,程序最高的工作时钟问题

时间:10-02

整理:3721RD

点击:

请教一下各位FPGA由晶振输入的时钟gclk,只是作为DCM输入,在其他各模块中没有用到,生成的60MHz时钟驱动其他模块

写了一个最简单的程序,

仅在top_module里例化了AD_module,即将AD的数据转换传入FPGA内,没有其他模块。

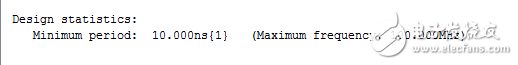

时钟约束后可跑的最快的时钟为100MHz,

--------------------------------------------------------------------------------

Design statistics:

Minimum period: 10.000ns{1} (Maximum frequency: 100.000MHz) --------------------------------------------------------------------------------整个程序非常的简单,时序约束报最高工作时钟却只有100MHz,查资料这款FPGA最快可跑四五百M,

时序约束也没有不满足建立时间和保持时间的报错,本身整个系统就用了一个时钟,同步设计

请教一下,为什么只能跑100MHz?是什么原因限制了呢?

另外,请教一下,时序报告中的,

+-------------------------------+-------------+-------------+-----

| | Period | Actual Period | | | Requiremen | Direct | Derivative | +-------------------------------+-------------+-------------+----- |TS_gclk | 25.000ns | 10.000ns| 5.190ns| +-------------------------------+-------------+-------------+----period requirement是25ns是因为我设置的是40MHz,请问一下后面的actual period里的direct 和derivative是什么意思呢?十分感谢!

写了一个最简单的程序,

仅在top_module里例化了AD_module,即将AD的数据转换传入FPGA内,没有其他模块。

时钟约束后可跑的最快的时钟为100MHz,

--------------------------------------------------------------------------------

Design statistics:

Minimum period: 10.000ns{1} (Maximum frequency: 100.000MHz) --------------------------------------------------------------------------------整个程序非常的简单,时序约束报最高工作时钟却只有100MHz,查资料这款FPGA最快可跑四五百M,

时序约束也没有不满足建立时间和保持时间的报错,本身整个系统就用了一个时钟,同步设计

请教一下,为什么只能跑100MHz?是什么原因限制了呢?

另外,请教一下,时序报告中的,

+-------------------------------+-------------+-------------+-----

| | Period | Actual Period | | | Requiremen | Direct | Derivative | +-------------------------------+-------------+-------------+----- |TS_gclk | 25.000ns | 10.000ns| 5.190ns| +-------------------------------+-------------+-------------+----period requirement是25ns是因为我设置的是40MHz,请问一下后面的actual period里的direct 和derivative是什么意思呢?十分感谢!

我是这么理解的,你给他设置40MHz的频率,FPGA给你一优化,给你跑到了100MHz,但是这100MHz不是说你这个程序或者说系统可以跑到的最大的频率。 你给他设置成200MHz,FPGA会给你再进行优化,直到优化不动了为止。其实就是说,FPGA有点比较说懒汉,你给他一个比较低的目标频率,他给你稍微改一改,一看满足要求了,他就不优化了,具体的你可以在时钟约束里面进行修改,查看下就知道了。

你好,FPGA工作的最高时钟取决于内部“最大延时路径”,就像“木桶效应”一样,你程序中有一个路径只能工作在100M,否则时序不满足,你可以通过工具的时序报告找出这个最大延时路径,然后优化

时钟用法有问题。

谢谢,我程序报告里的最大工作时钟的确是跟我约束的值有关~