FPGA时序逻辑延后一个周期怎么解决

时间:10-02

整理:3721RD

点击:

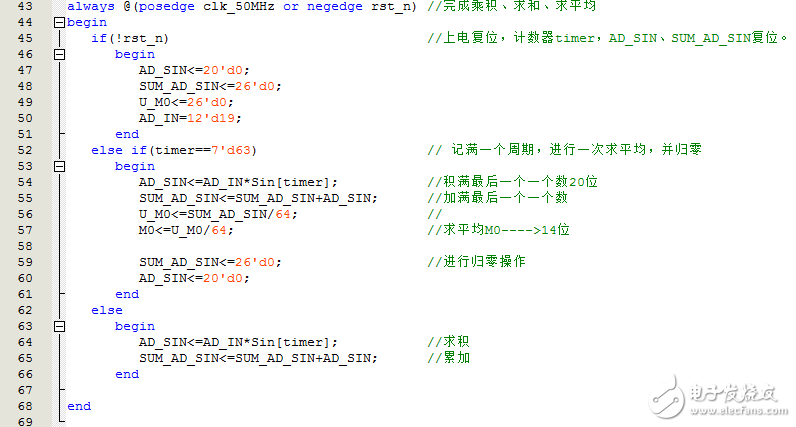

大神求救!我现在想要用FPGA实现一个数与一个数组(宽度为64)数相乘,累加,再取平均,用的是时序逻辑加上非阻塞赋值的方法实现,即从数组0开始相乘,一直到数组63,当乘完63时,将累加的数取平均输出,但问题是,最后数组63相乘这一步就是没有实现,我看网上说是时序逻辑会延后一个时钟周期导致最后一步没有加上,我试着将程序中timer==7‘d63改为timer==7‘d64,最后一个就加上了,但这样的话,新的问题又来了,我希望64个周期算完的,却要65个周期,这要什么方法解决这个问题?

怎么没有看到timer的初值啊

M0 >>

用assign语句输出,可提前一周期。不建议直接除法,除法可以用截位来实现