想调用一下vivado里IP核的clock wizard模块,输入时钟为50M,输出为25M。

时间:10-02

整理:3721RD

点击:

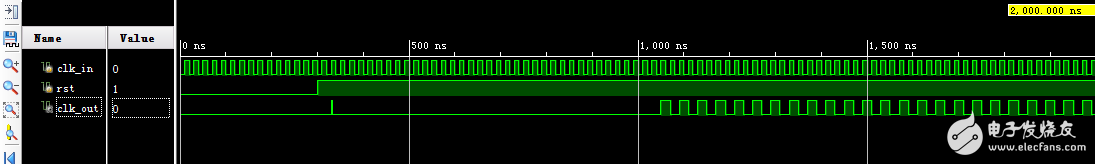

想测试一下vivado里IP核的clock wizard模块,模式为输入时钟为50M,输出为25M。仿真波形如图所示:有一个问题不明白,就是为什么输出时钟在前面较长一段时间始终输出低电平且存在毛刺。以下是我的仿真代码:

module phase_shift_simu;

reg clk_in;

reg rst;

wire clk_out;

phase_shift phase_shift_simu(

.clk_in(clk_in),

.rst(rst),

.clk_out(clk_out)

);

initial

begin

clk_in = 0;

rst = 0;

#300;

rst = 1;

end

always #10 clk_in = ~clk_in;

endmodule

module phase_shift_simu;

reg clk_in;

reg rst;

wire clk_out;

phase_shift phase_shift_simu(

.clk_in(clk_in),

.rst(rst),

.clk_out(clk_out)

);

initial

begin

clk_in = 0;

rst = 0;

#300;

rst = 1;

end

always #10 clk_in = ~clk_in;

endmodule

这个你要看一下锁相环的原理了,好3个部分组成,什么什么和什么。忘了!

所以说,这个是正常的,或者说原理就是这样的,而不是我代码的问题或是其他什么?

不是,你又改不了ipcore的代码,一般ipcore不会出错的,pll你只要保证工作时lock上了并且稳定就没问题

我是指仿真代码啊

没问题啊!不过一般pll都有一个lock信号,仿真的时候也能看到lock一直为高!

好吧,谢啦

你的仿真代码里也没例化clock wizard模块啊