求帮忙设计一个同步串行数据发送电路

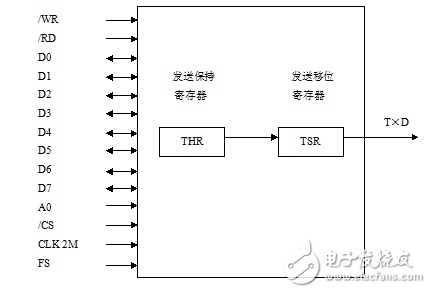

系统结构如图:

/WR: 写信号

/RD: 读信号

D0~D7: 双向数据线

A0: 地址线

/CS: 片选信号

假定以上信号同Intel8086,8031读、写时序兼容。

Clock: 时钟(本例中假定为2.048Mhz)

FS: 同步信号,发送端T×D的bit流应与FS同步。

上图是实现下述功能的数据发送框图,发送部分由发送保持寄存器和发送移位寄存器组成。

n 发送保持寄存器定义了两种状态:空、满。

n 发送保持寄存器的数据写入端口为00H。

n 发送保持寄存器的状态读出端口为00H。

功能如下:

1.当THR不满时,可以向THR中写入数据,一旦TSR空而THR中有数据时,THR中的数据就送到TSR,TSR中的数据以串行方式从T×D端发出,高位在前,并要求在T×D的比特流中若连续出现5个“1”,则在5个连续“1”后自动插入一个“0”。

(注意:)相邻两个字节之间也会出现5个连续“1”。

2.以同步信号FS开始连续发送四个字节。字节内容由用户通过口地址00H写入。之后,T×D线路为空闲;下一个同步信号开始时,又连续发四个字节,字节内容由用户通过口地址00H写入,以此类推。

3.当无字节发送(即T×D线路空闲时),发送“7EH”(01111110),这时出现5个连续的“1”之后,不用填充“0”。

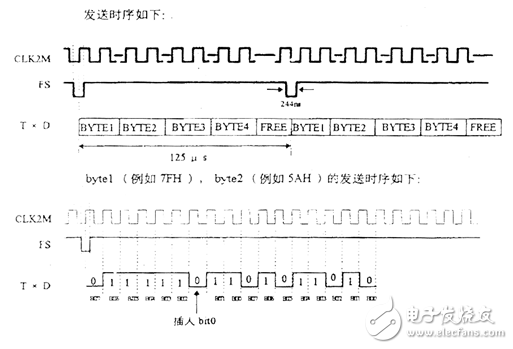

发送时序如下:

说明:

(1)CLK 2M为占空比为50%的2.04MHz的时钟,从CLK 2M的上升沿开始每个比特的发送。

(2)FS为T×D端串行比特流的同步信号。在FS为低电平时,CLK 2M的上升沿开始发送第一个字节。

(3)FS的周期为125μs,低电平宽度为244ns,FS的下降沿处在CLK 2M的低电平的中央,FS的上升沿处在CLK 2M高电平的中央。

可以有偿帮你做,有兴趣请联系QQ:865021481

好银啊!,太感谢!

同学,你是西工大的吧

请问这个您帮她做了吗?

不记得了。你也要做吗?