(新人求助),Quartus ii 的 Verilog 设计,怎么把自己的底层文件添加到顶层?

作为初学者,今天编写了几个 底层的 .V 程序,然后又编写顶层的.v顶层文件,可是,总是找不到添加的方法,

百度了好久,也没找到,求助大神们,怎么添加?

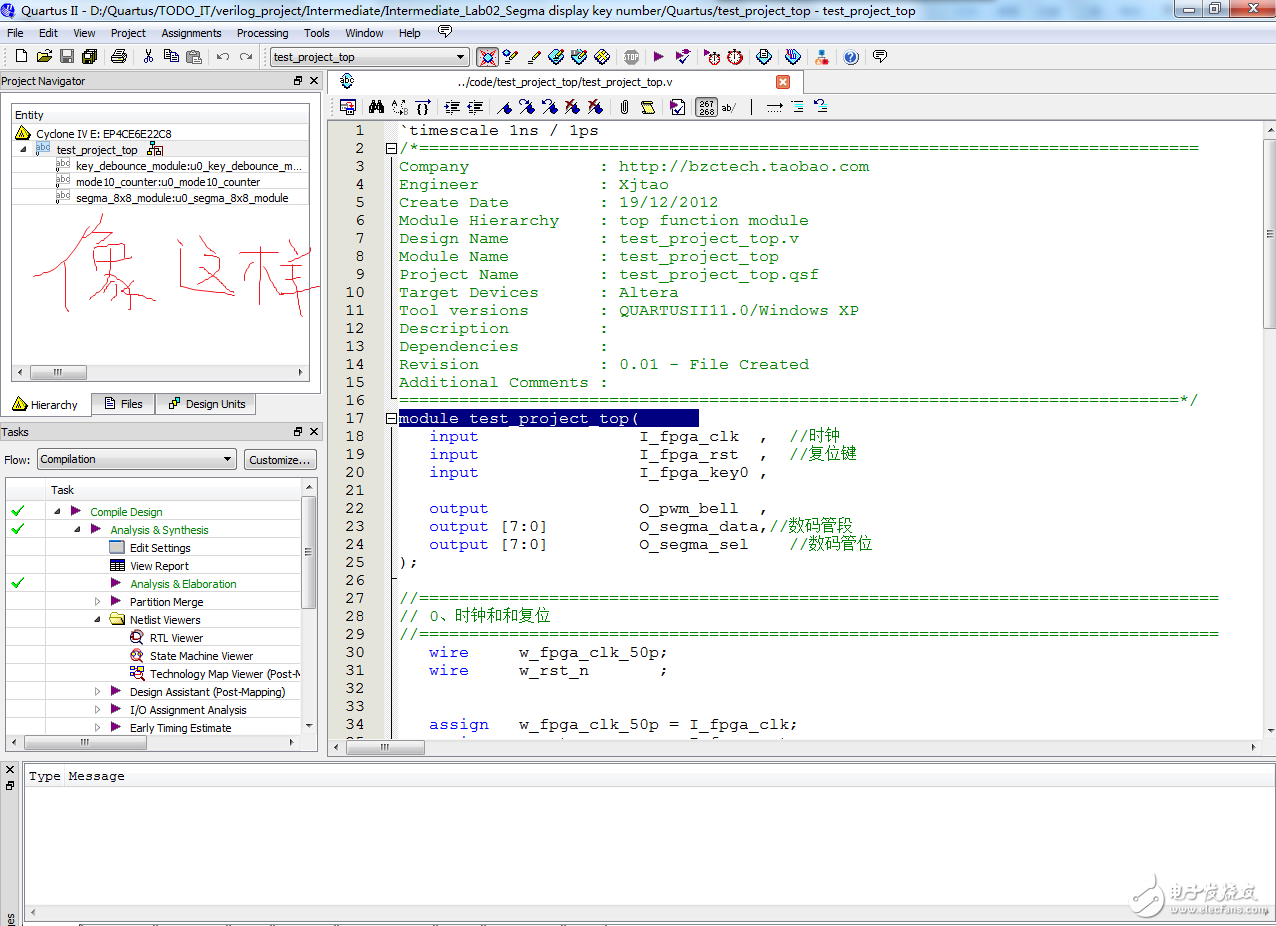

我的意思是这样的 顶层调用底层

1

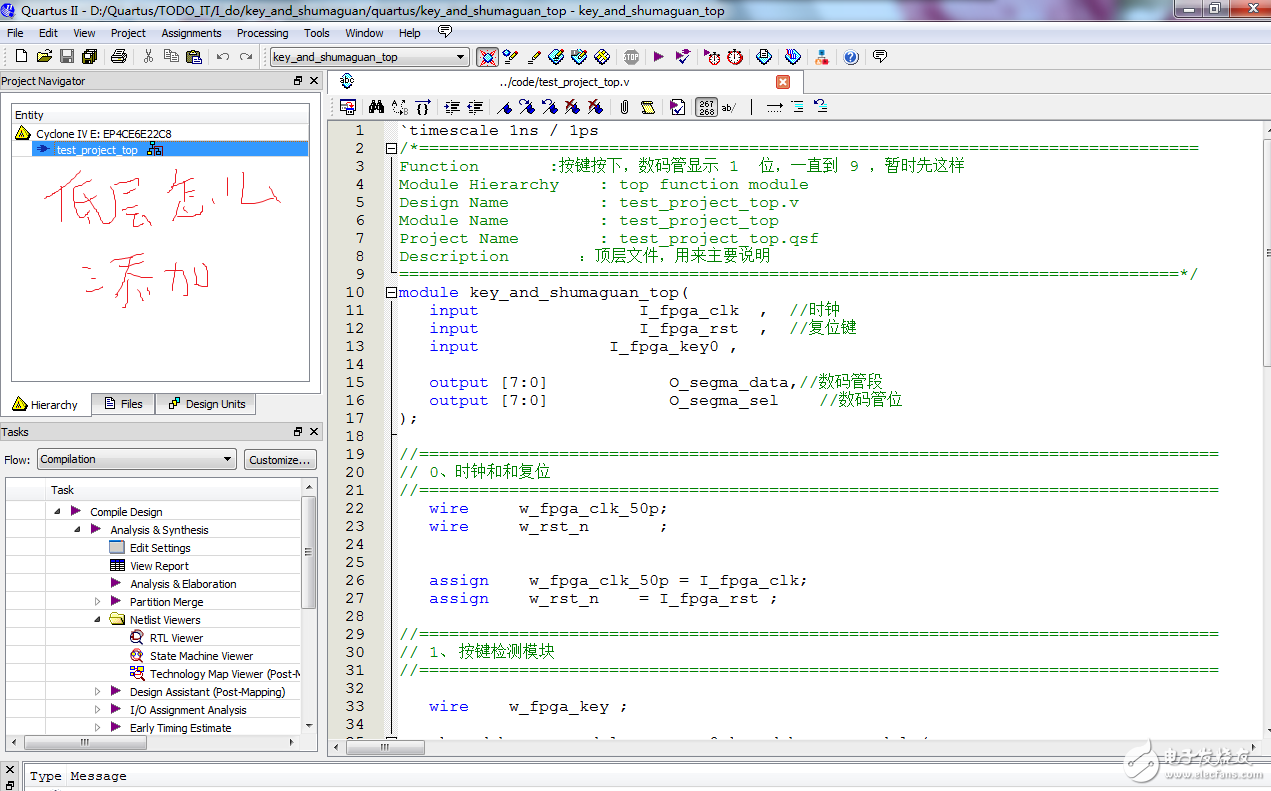

我的意思是这样

你可以看一下Verilog数字系统设计教程,夏宇闻版,上面有提到,通过,.clk(clk)这样类似的方式,把底层文件添加到顶层文件上

把顶层文件 编译一下,底层文件都自动到下面~~

终结此贴

小编怎么弄得,不行呀

就是例化吧,在顶层调用底层文件

顶层源代码:

/*序列检测器verilog HDL源程序*/

module series_det(rstn,din,b);//模块定义,模块名为series_det,端口为rstn,din,b

input rstn;//定义位长为1的输入端口rstn

input [6:0]din;//定义位长为7的输入端口 din

output b;//定义位长为1的输出端口b

reg b;//设置端口类型为寄存器类型

parameter s0=0,s1=1,s2=2,s3=3,s4=4,s5=5,s6=6;//定义常数参数,用以表征状态机的7个状态

reg [2:0]s;//状态标识位,选择3位寄存器表征不同的状态

always @(rstn)//always语句,只要事件触发一次,always就执行一次

case(s)//case语句,根据s的不同状态选择不同的语句执行位置

default://默认语句,一个case语句中至多有一个default语句

begin s<= s0;b<=0;end//默认返回s0状态

s0:

if(din[0]) begin s<=s1;b<=0;end//if-else语句,din[0]为真时,令状态标识位s为s1状态,

else begin s<=s0;b<=0;end //输出b为0;当din[0]为假(0)时,s转移至s0状态,

s1: //输出b为0。过程中均采用非阻塞赋值方法。下同。

if(din[1]) begin s<=s2;b<=0;end

else begin s<=s0;b<=0;end

s2:

if(din[2]) begin s<=s3;b<=0;end

else begin s<=s0;b<=0;end

s3:

if(din[3]) begin s<=s3;b<=0;end

else begin s<=s4;b<=0;end

s4:

if(din[4]) begin s<=s1;b<=0;end

else begin s<=s5;b<=0;end

s5:

if(din[5]) begin s<=s6;b<=0;end

else begin s<=s0;b<=0;end

s6:

if(din[6]) begin s<=s2;b<=0;end

else begin s<=s0;b<=1;end

endcase //case结束语句

endmodule //模块结束语句,必不可少

/*七段数码管程序*/

module seg7_lut(oSEG1, oSEG2, oSEG3, oSEG4, oSEG5, oSEG6, oSEG7, din);//定义模块,指定

input [6:0] din;//定义7位输入端口din //输入输出端口

output [6:0] oSEG1, oSEG2, oSEG3, oSEG4, oSEG5, oSEG6, oSEG7;//输出端口指定

reg [6:0] oSEG1, oSEG2, oSEG3, oSEG4, oSEG5, oSEG6, oSEG7;//输出端口为寄存器类型

always @(din)

begin

case(din[0]) //数码管显示。当输入din[0]为1是,执行第一条语句,令七段

1'h1:oSEG1=7'b1111001; //共阳极数码管显示数字“1”,否则显示“0”。下同。

1'h0:oSEG1=7'b1000000;

endcase

case(din[1])

1'h1:oSEG1=7'b1111001;

1'h0:oSEG1=7'b1000000;

endcase

case(din[2])

1'h1:oSEG1=7'b1111001;

1'h0:oSEG1=7'b1000000;

endcase

case(din[3])

1'h1:oSEG1=7'b1111001;

1'h0:oSEG1=7'b1000000;

endcase

case(din[4])

1'h1:oSEG1=7'b1111001;

1'h0:oSEG1=7'b1000000;

endcase

case(din[5])

1'h1:oSEG1=7'b1111001;

1'h0:oSEG1=7'b1000000;

endcase

case(din[6])

1'h1:oSEG1=7'b1111001;

1'h0:oSEG1=7'b1000000;

endcase

end

endmodule

求问一下这个顶层怎么调用低层

每一个底层.v都是一个函数,有输出也有输入。就像C语言中调用函数一样,把底层的头文件,放到顶层里面,把输入输出跟顶层文件输入输出对应上,编译一下,就可以了。

直接在顶层文件里调用就行了啊,多看看书吧。

多看看基础语法再写代码吧