我要在testbench中读入一个外部文件作为输入信号,在modelsim仿真中,显示的输入信号一直为 未知 求解中!

总是显示读取数据失败 代码没看出什么问题 哪位大神救救我吧

解决了 还得心细 啊

你好,请问你是怎么解决的,方便贴一下代码吗?谢谢

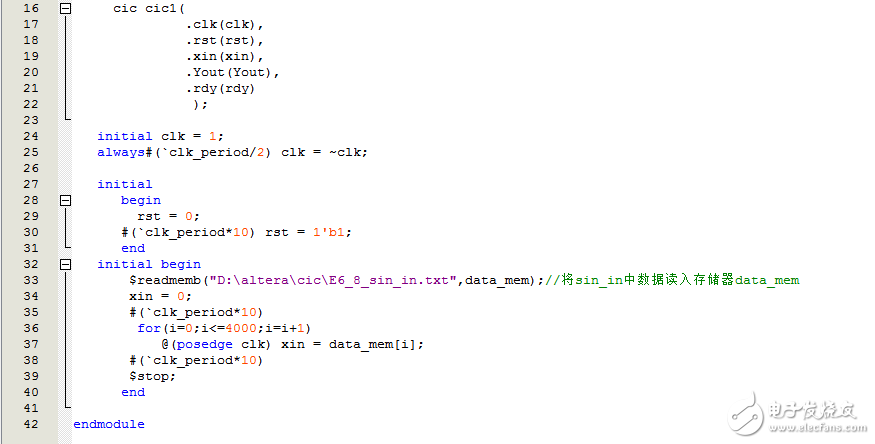

cic cic1(

.clk(clk),

.rst(rst),

.xin(xin),

.Yout(Yout),

.rdy(rdy),

.intout(intout),

.dout(dout),

.yt(yt)

);

initial clk = 1;

always#(`clk_period/2) clk = ~clk;

initial

begin

rst = 0;

#(`clk_period*5) rst = 1'b1;

end

initial begin

$readmemb("D:/altera/cic/E6_8_sin_in.txt",data_mem);//将sin_in中数据读入存储器data_mem

xin = 0;

#(`clk_period*10)

for(i=0;i<=4000;i=i+1)

@(posedge clk) xin = data_mem;

//#(`clk_period*10)

$stop;

end

//滤波器输出信号写入文件

initial

begin

fid = $fopen("D:/altera/cic/sin_out.txt");

for(j=0;j<=800;j=j+1)

@(negedge rdy)

$fdisplay(fid,"%d",Yout);

if(j == 800)

$fclose(fid);

end

我是新手可能问的有点基础,你的intout和dout分别是什么接口。我最近正在学习FPGA的FIR滤波器。谢谢

这是testbench里面的例化,它们接的是上一级的输出以及下一级的输入,中间信号

还有一个问题 ,你贴出来的正确代码中 data_mem和i都没有定义啊 testbench怎么仿真通过的?

这个只是testbench中主要的部分代码,端口定义没有贴出来,下面所使用到的端口都定义了,不然肯定出不了结果啊

小编方便把其他的也贴出来吗?学习一下。谢谢

小编 我还有其他问题不明白,能不能加个QQ学习一下啊,我的QQ578240076,谢谢。