FPGA时钟约束问题

时间:10-02

整理:3721RD

点击:

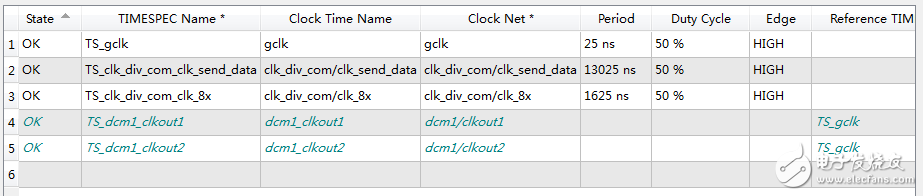

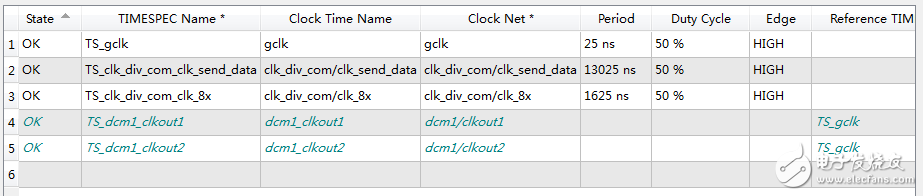

FPGA的DCM模块,40MHz时钟输入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。

对40MHz时钟添加了约束,系统不是会自动对三个输出时钟进行约束的吗?

编译后发现只对clkout1 40MHz,clkout2 60MHz进行了约束?

这样是对的吗?

请各位指点一二,谢谢。

对40MHz时钟添加了约束,系统不是会自动对三个输出时钟进行约束的吗?

编译后发现只对clkout1 40MHz,clkout2 60MHz进行了约束?

这样是对的吗?

请各位指点一二,谢谢。

是锁相环吗?如果不是锁相环要自己用generate clock来约束,如果是用drive all神马来着 ,记不起来了,网上能找到!

谢谢!

我这个是xilinx系列的clocking wizard得到的dcm,也是属于锁相环。百度drive all 应该是针对altera公司的。请问针对xilinx怎么解决呢?

1111111111111111111111111111111111111

好像也有一个类似的指令把,具体记不清了,你百度一下吧!

好的,十分谢谢~