关于边沿检测的问题

时间:10-02

整理:3721RD

点击:

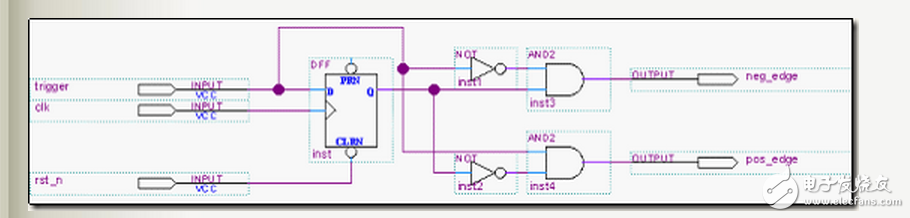

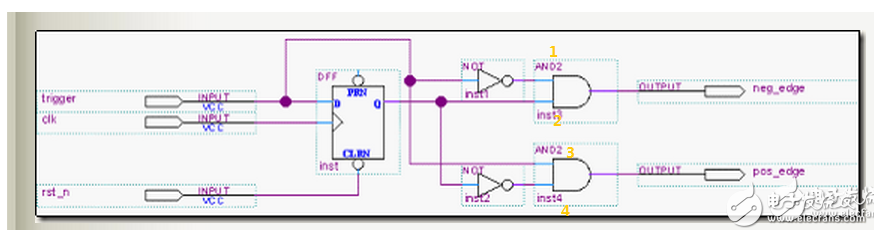

入图,有没有大神分析一下,是怎实现边沿检测的,它各个时期的电平状态是什么

边沿检测

以CLK为基准判断trigger的上升、下降沿

①输入为0(D触发器输出0),变到1后,3口为1,D触发器在下一个CLK上升沿之前保留上一个值,为0,非之后为1,3口与4口相and输出1,代表上升沿。

②输入为1(D触发器输出1),变到0后,非之后1口为1,D触发器在下一个CLK上升沿之前保留上一个值,为1,1口与2口相and输出1,代表上升沿。

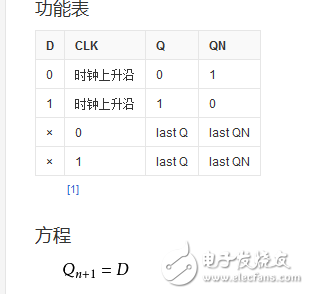

D触发器

就是延时一拍,如果打一拍为低,正常为高则为上升沿,类似判断下降沿

②输入为1(D触发器输出1),变到0后,非之后1口为1,D触发器在下一个CLK上升沿之前保留上一个值,为1,1口与2口相and输出1,代表上升沿。

第二点 最后那块 应该是代表 下降沿吧

学习一下,,,,,,,,,,

进来学习一下下了哦,