求问!双口RAM读数据的时候为什么有延时

时间:10-02

整理:3721RD

点击:

从双口ram里读数据的时候一直有两个时钟的延时?

图1

图2

图1红色方框内的是输入地址寄存器,所以从你外部输入读地址到RAM内部锁存该地址需要一个时钟周期。

重点的是蓝色部分,Read output ports选项,图2是勾选该选项后的参数页,可以看到输出端多了一级寄存器,对数据输出打了一拍,这样的好处是输出是同步的而不是异步的。

所以如果不勾选Read output ports选项时,读数据比读地址滞后一个时钟,但是读数据是异步的;

勾选该选项时,异步输出经过输出寄存器后,又多了一个时钟周期,具体的可以看官方给时序图,如下

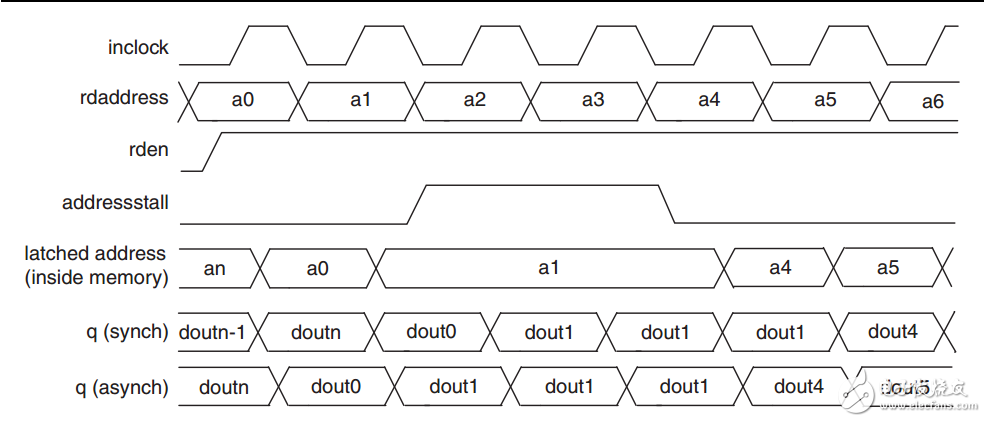

读和写公用一个inclock时钟,addressstal是时钟使能,低有效,latched address就是地址寄存器。

q(asynch)为输出寄存器之前的异步信号,q(synch)为输出寄存器之后的同步输出信号。可以看到q(synch)比读地址慢了两个时钟周期。

Ps:第一次回答,有错误欢迎指正

以我比较熟悉的Altera(现在是Intel了= =)的双口RAM IP核为例,在参数设置的过程中,有一页如下图

图1

图2

图1红色方框内的是输入地址寄存器,所以从你外部输入读地址到RAM内部锁存该地址需要一个时钟周期。

重点的是蓝色部分,Read output ports选项,图2是勾选该选项后的参数页,可以看到输出端多了一级寄存器,对数据输出打了一拍,这样的好处是输出是同步的而不是异步的。

所以如果不勾选Read output ports选项时,读数据比读地址滞后一个时钟,但是读数据是异步的;

勾选该选项时,异步输出经过输出寄存器后,又多了一个时钟周期,具体的可以看官方给时序图,如下

读和写公用一个inclock时钟,addressstal是时钟使能,低有效,latched address就是地址寄存器。

q(asynch)为输出寄存器之前的异步信号,q(synch)为输出寄存器之后的同步输出信号。可以看到q(synch)比读地址慢了两个时钟周期。

Ps:第一次回答,有错误欢迎指正