例说FPGA连载95:基于HDMI的AV采集显示之功能概述

时间:10-02

整理:3721RD

点击:

例说FPGA连载95:基于HDMI的AV采集显示之功能概述

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

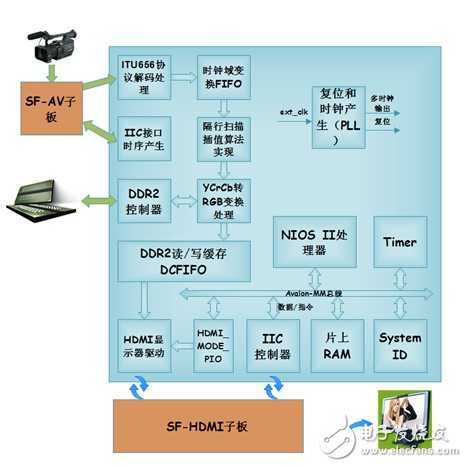

本实例系统功能框图如图19.1所示。以NIOS II处理器为主构建一个基本的嵌入式系统。IIC控制器外设为自定义组件,通过Avalon-MM总线连接到NIOS II处理器,NIOS II处理通过对IIC控制器的访问实现HDMI控制器芯片ADV7513的初始化配置;HDMI_MODE_PIO组件连接到HDMI显示驱动模块,NIOS II处理器可以通过该模块实现在线的HDMI驱动时钟和分辨率的动态切换。逻辑部分实现AV视频信号的解码、时域变换、去隔行处理、视频流缓存以及HDMI显示驱动。本实例只有一路AV视频输入,但是在HDMI显示器上,我们将这一路分辨率为640*480的AV视频图像进行复制,在分辨率为1280*960的HDMI显示器上显示出4个完全一样的AV视频图像,即所谓的“一拖四”。

图19.1 工程实例17功能框图

还没学习到那么深入,来支持下

这个肯定是好资料哦