quartus ii 9.0 verilog 仿真报错,求助

时间:10-02

整理:3721RD

点击:

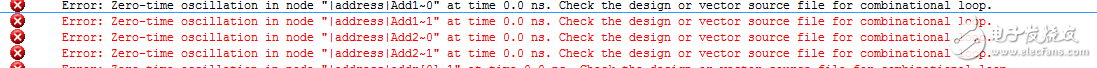

编译通过,仿真报错如下不知为何?大神们,帮我快看看,万分感谢!

Error: Zero-time oscillation in node "|address|Add1~0" at time 0.0 ns. Check the design or vector source file for combinational loop.

代码如下:

module address(dir,clk,div,addr);

input clk,dir;

input[8:0] div;

output[8:0] addr;

reg[1:0] count_addr;

reg[48:0] count;

reg fenpin_clk;

reg[8:0] addr;

always @(negedge clk)

begin

count=count+1;

if(count==500000) //fenpin 20ms

begin

count=0;

fenpin_clk=~fenpin_clk;

end

end

always @(negedge clk )

begin

if(dir==0)

begin

count_addr=count_addr+1;

if(count_addr>=2)

count_addr=0;

end

end

always @(count_addr)

begin

case(count_addr)

0:addr=addr+div;

1:addr=addr-div;

default:addr=addr+div;

endcase

end

endmodule

Error: Zero-time oscillation in node "|address|Add1~0" at time 0.0 ns. Check the design or vector source file for combinational loop.

代码如下:

module address(dir,clk,div,addr);

input clk,dir;

input[8:0] div;

output[8:0] addr;

reg[1:0] count_addr;

reg[48:0] count;

reg fenpin_clk;

reg[8:0] addr;

always @(negedge clk)

begin

count=count+1;

if(count==500000) //fenpin 20ms

begin

count=0;

fenpin_clk=~fenpin_clk;

end

end

always @(negedge clk )

begin

if(dir==0)

begin

count_addr=count_addr+1;

if(count_addr>=2)

count_addr=0;

end

end

always @(count_addr)

begin

case(count_addr)

0:addr=addr+div;

1:addr=addr-div;

default:addr=addr+div;

endcase

end

endmodule

是count_addr和addr没有赋初值吧?

always @(count_addr)里面count_addr不是时钟不要用它触发;addr=addr+div自己加一个变量给自己容易出latch,应该按照功能看看能不能改成位运算,移位之类的操作。