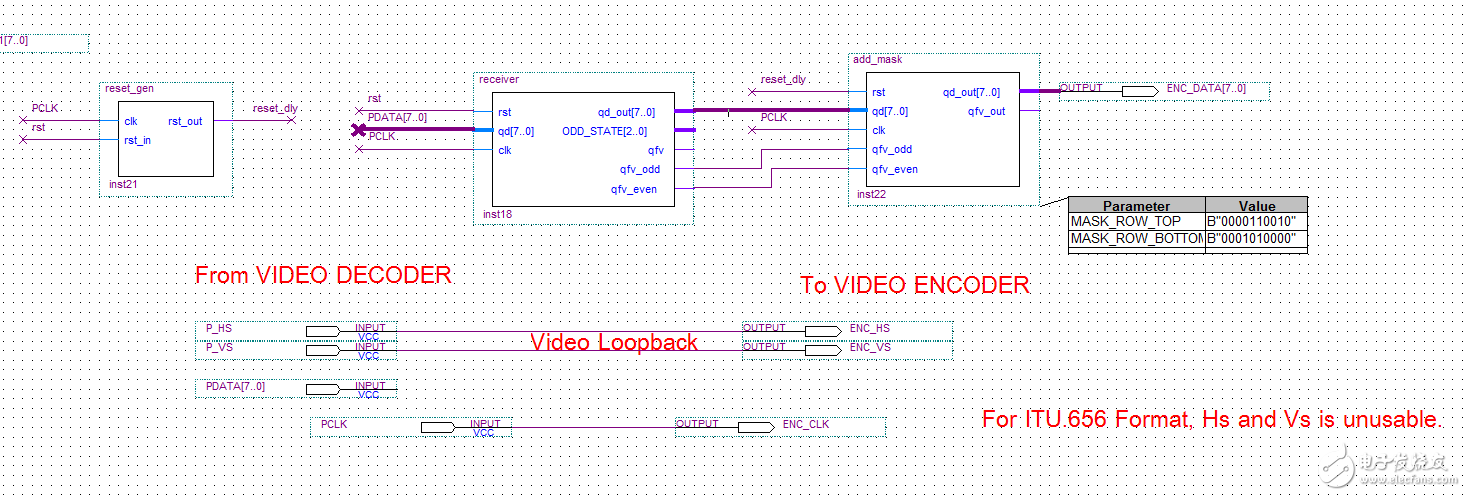

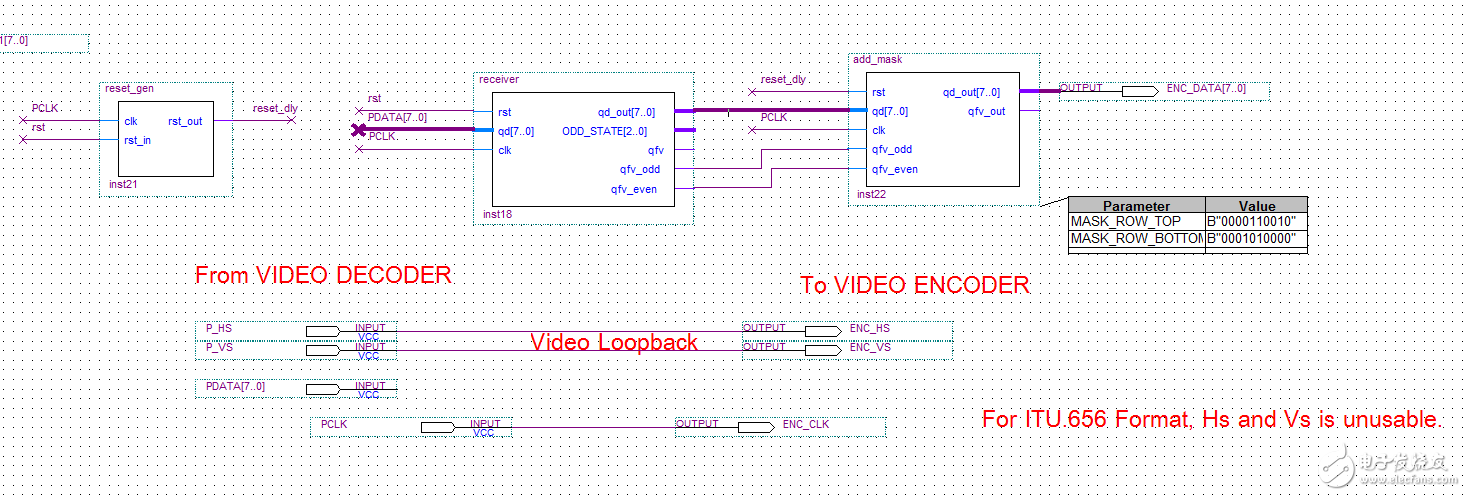

SAA7113输出的是ITU656格式,SAA7121输入的也是ITU656格式,为什么不能直接相连

时间:10-02

整理:3721RD

点击:

SAA7113输出的是ITU656格式,SAA7121输入的也是ITU656格式,为什么不能直接相连,要加上一个verilog写的解码模块receiver

- module receiver(

- rst,

- qd,

- clk,

-

- qd_out,

- qfv,

- qfv_odd,

- qfv_even,

- ODD_STATE

- );

- /*** ports ***/

- input rst;

- input [7:0] qd;

- input clk;

- output [7:0] qd_out;

- output [2:0] ODD_STATE;

- output qfv,qfv_odd,qfv_even;

- //internal

- reg [7:0] qd_dly,qd_dly1,qd_dly2;

- always @ (posedge clk) begin

- qd_dly <= qd;

- qd_dly1 <= qd_dly;

- qd_dly2 <= qd_dly1;

- end

-

- reg [2:0] ODD_STATE;

- always @ (posedge clk or negedge rst)

- if(!rst) begin

- ODD_STATE <= 0;

- end

- else

- case(ODD_STATE)

- 3'd0: if(qd_dly==8'hff)

- ODD_STATE <= 3'd1;

- else

- ODD_STATE <= 3'd0;

- 3'd1: if(qd_dly==8'h00)

- ODD_STATE <= 3'd2;

- else if(qd_dly==8'hff)

- ODD_STATE <= 3'd1;

- else

- ODD_STATE <= 3'd0;

- 3'd2: if(qd_dly==8'h00)

- ODD_STATE <= 3'd3;

- else

- ODD_STATE <= 3'd0;

- 3'd3: if(qd_dly==8'h80)

- ODD_STATE <= 3'd4;

- else if(qd_dly==8'h9d)

- ODD_STATE <= 3'd5;

- else if(qd_dly == 8'hc7)

- ODD_STATE <= 3'd6;

- else if(qd_dly == 8'hda)

- ODD_STATE <= 3'd7;

- else

- ODD_STATE <= 3'd0;

- 3'd4: ODD_STATE <= 1'b0;

- 3'd5: ODD_STATE <= 1'b0;

- 3'd6: ODD_STATE <= 1'b0;

- 3'd7: ODD_STATE <= 1'b0;

- endcase

-

- reg [10:0] qfv_cnt;

- reg qfv_odd;

- always @ (posedge clk or negedge rst)

- if(!rst)

- qfv_odd <= 1'b0;

- else if(ODD_STATE == 3'd4)

- qfv_odd <= 1'b1;

- else if(qfv_cnt == 11'd1439)

- qfv_odd <= 1'b0;

-

- reg qfv_even;

- always @ (posedge clk or negedge rst)

- if(!rst)

- qfv_even <= 1'b0;

- else if(ODD_STATE == 3'd6)

- qfv_even <= 1'b1;

- else if(qfv_cnt == 11'd1439)

- qfv_even <= 1'b0;

- wire qfv = qfv_even | qfv_odd;

- always @ (posedge clk or negedge rst)

- if(!rst)

- qfv_cnt <= 1'b0;

- else if(qfv)

- qfv_cnt <= qfv_cnt + 1'b1;

- else

- qfv_cnt <= 1'b0;

-

- wire [7:0] qd_out = qfv ? qd_dly : qd_dly1;

- endmodule