例说FPGA连载87:工业现场实时监控界面设计之LCD显示驱动模块代码解析

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

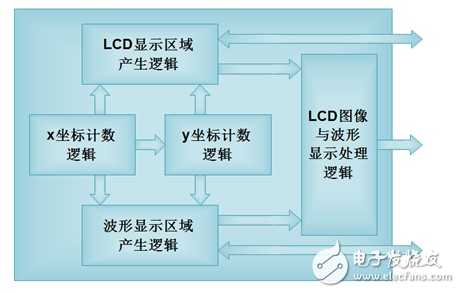

该模块除了实现正常的LCD驱动显示逻辑,还需要实现LCD图像的数据读出控制信号产生、波形数据点的读出控制信号产生,并对LCD当前显示像素点的多个显示数据做仲裁判断,以显示我们所期望的正确色彩。该模块的功能框图如图17.15所示。

图17.15 LCD显示驱动模块功能框图

波形显示的X坐标有效区域(wave_xs,wave_xe)区域内,产生双口RAM的数据读请求信号wave_rden。之所以(wave_xs,wave_xe)区域内都需要读取当前对应的波形点,是由于波形点的数据本身决定了它处于(wave_ys,wave_ye)的具体位置,我们无法预测,所以只能在整个x轴显示区域读取并作判断。这部分设计的逻辑代码如下。

reg wave_rden; //双口RAM读使能信号

always @(posedge clk or negedge rst_n)

if(!rst_n) wave_rden ={2'd0,wave_xs}+(VGA_HST+VGA_HBP-5)) && (xcnt wave_datbus)

if((ycnt >=(VGA_VST+VGA_VBP)+({2'd0,wave_ye}-(wave_datbusr-1'b1)))

&& (ycnt =(VGA_VST+VGA_VBP)+({2'd0,wave_ye}-(wave_datbus-1'b1)))

&& (ycnt<= (VGA_VST+VGA_VBP)+({2'd0,wave_ye}-(wave_datbusr-1'b1)))) lcd_djdbr <=wave_fcor; //前景色

else lcd_djdbr <=wave_bcor; //背景色

end

end

end

else lcd_djdbr <= lcd_djdb;