关于quartus例化ip ram或者rom的问题

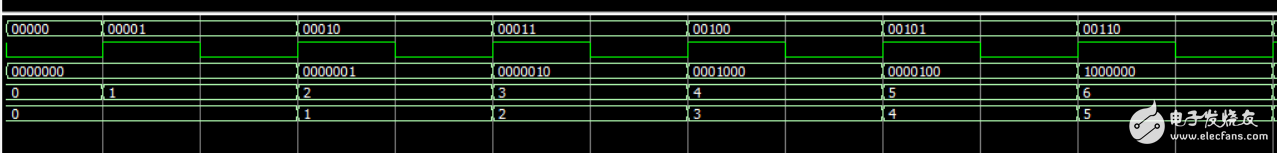

图2

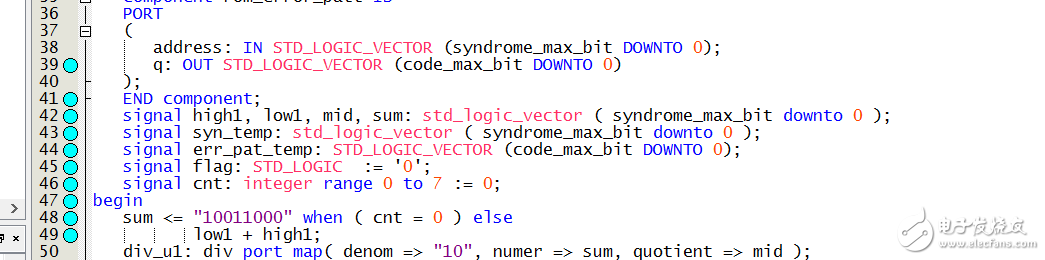

上面看不到输入输出address是输入,q是输出

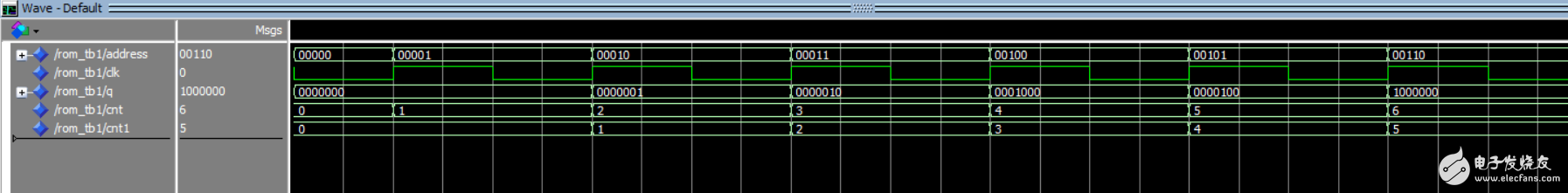

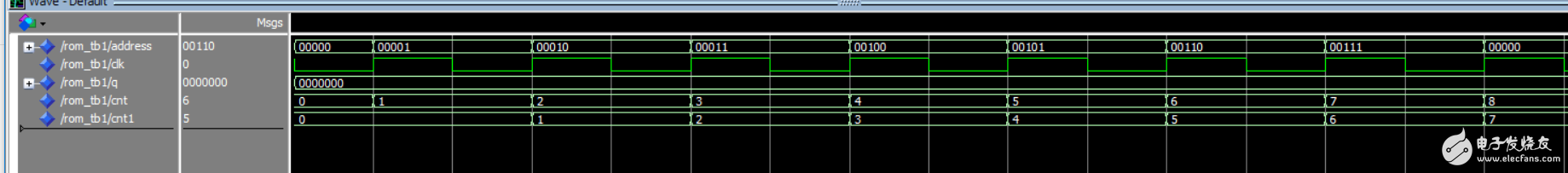

图1

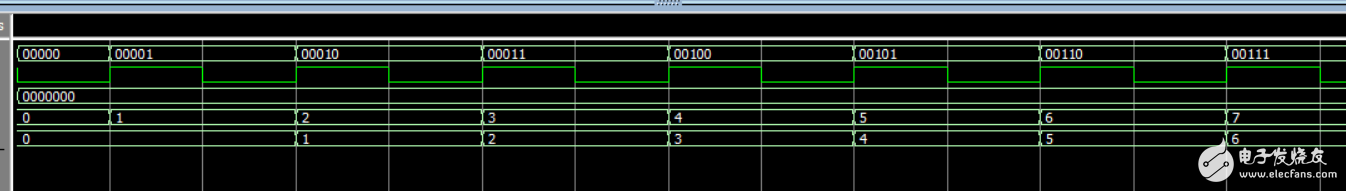

图2

这个延时时去不掉的,如果你在设置RAM ip核时把register q选中的话再看你的RAM输出,你会发现延时两个时钟,这是因为输出加了一级寄存器,而对应当前有一级延时是因为ram内部对你的地址做了一个寄存。

ssdgsb

嗯 请问你知道图中 在quartus里面设置像断点一样的点 也是调制用的吗?是用它自带的还是上面工具?

就是想问是像软件可以一步一步debug调试用的吗

这个应该就是简单的代码标记而已,为了方便代码之间进行跳转用的,并不能进行调试,实际没用过

前面那个时钟的问题 要用它自带好像是有延迟 因为我现在是用rom 在处理数据时我不需要对ram进行写入或更新 所以我用的应该算rom 但是自己写也行 系统的就是用那个mif初始话特别好用 如果要读取mif这个文件的话 必须用quartus自带的 那就涉及时钟 就会延迟了 如果能有办法改它那个读取的程序就好了

先看一下RAM ipcore的特征,在配置时先看一下配置方式就是有锁存器

在生成的ipcore中

altsyncram_component.outdata_reg_a ="UNREGISTERED",就是无寄存器

altsyncram_component.outdata_reg_a ="CLOCK0",就是有寄存器

发现连了时钟线的就是有锁存器,没连时钟线的就是没锁存器。很可能有时钟触发的就是always@(edge clk),没有时钟就是assign A=B,所以有时钟触发里有锁存器,没有就是总线输入输出,没锁存器。

我之前写过一篇帖子是讲这个的,如果你感兴趣,可以一起交流一下

http://bbs.elecfans.com/forum.php?mod=viewthread&tid=1104760&extra=

把中间的两个符号去掉

谢谢。 但是我看程序例化自带的rom,outdata_reg_a => "unreigsteded", 仍然有一个时钟周期的延迟 我使用这个rom很简单 只要我给个地址 它把对应的值输出即可 但自己写的话 使用内存小的时候 工作频率还过得去 内存大了 就会慢很多。 另外 想问你个其它问题 我用的altera stratix 4, 它自身有大概20Mb的内存 现在我才使用50% 他就综合不过 是不是我选的内存类型不对(我选的auto 不知道具体选那个) 如果你有这个经验 麻烦告诉一声 谢谢。

嗯,要一个时钟延时,是很正常的了。

好的,之前的账户密码弄丢了,这段时间一直在弄论文的东西,有点烦,等搞完这个我们一起看一下

这个延时是去不掉的,是IP核本身特性;另外我认为如果去掉时钟ip核就不会被驱动,也就没有数据