例说FPGA连载75:FX2与FPGA之SignalTap II与功能概述

时间:10-02

整理:3721RD

点击:

例说FPGA连载75:FX2与FPGA之SignalTap II与功能概述

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

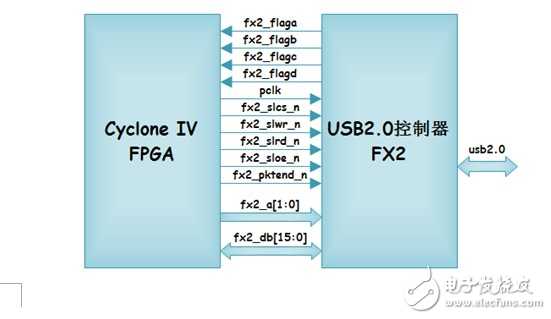

FPGA和FX2芯片之间的SlaveFIFO接口如图14.13所示,这26个有效信号线(fx2_flagb和fx2_flagc信号线实际上并没有使用)若是使用传统的逻辑分析仪进行检测,恐怕连线的工作就要折腾我们一个大半天,况且更痛苦的是我们的电路板上貌似还没有留出专门的测试点供连接,这就使得这些信号的观察难上加难。

图14.13 SlaveFIFO接口连接

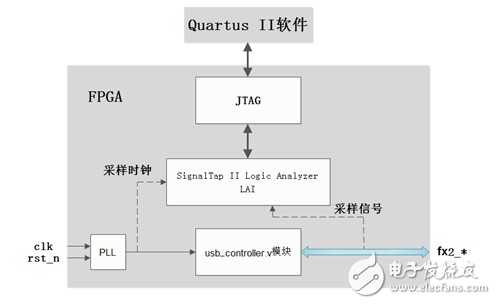

怎么办?FPGA的可编程特性此时要发挥出强大的优势了,它甚至灵活到在线调试的手段都能够“可编程”为设计的一部分。该例程我们将要通过FPGA器件内部例化一个In-System Logic Analyzer进行在线的板级调试。这个In-System Logic Analyzer有个很帅气的名字叫做“SignalTapII”。

如图14.14所示,我们这个在线逻辑分析仪内嵌在了FPGA中,借助于PLL产生的时钟信号fx2_pclk作为采样时钟,与FX2连接的其它信号将作为被采样信号连接到在线逻辑分析仪中。通过JTAG线缆,我们在PC端的Quartus II中将会观察到这些信号的波形。

图14.14 In-System LogicAnalyzer功能框图