基于FPGA的高速以太网适配器卡必备的PCIe Gen3技术

时间:10-02

整理:3721RD

点击:

INVEA-TECH公司制作了基于FPGA的硬件加速以太网接口卡(HANICs)。该公司在加利福尼亚圣克拉拉以太网技术峰会上展示了两款高速以太网适配器卡—COMBO 80G和最近发布的COMBO 100G,它们都着重使用了板级FPGA和光学以太网模块。这两块卡都采用了相同的基础硬件架构。首先,高速以太网数据流通过适当的光口进入适配器卡,然后在板级FPGA中进行处理,主要是实现各种网络监控和加速的任务。最后,处理好的数据流通过一个PCIe Gen3接口发送到主系统,或者通过光以太网连接发送回去。

下面详细描述了这两块卡的区别:

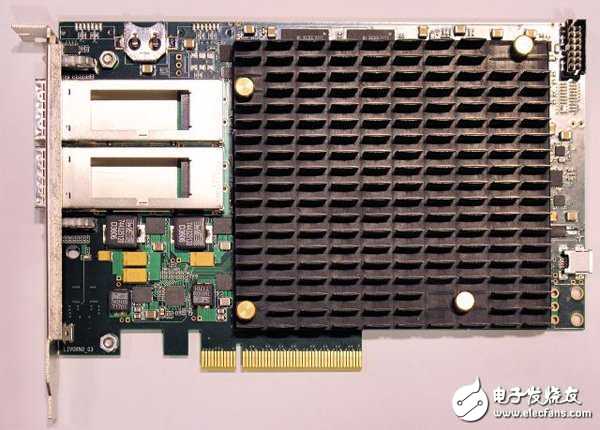

INVEA-TECH COMBO 80G HANIC可以连接两个40Gbps QSFP+ 光纤(或者铜质)以太网收发器模块。一个板级的Virtex-7 690T FPGA用于接收以太网数据流,该FPGA通过4个工作在10Gbps的GTH 13.1Gbps SerDes来跟两个QFSP+模块通信。FPGA内部的可编程硬件逻辑用于处理以太网数据流中的数据包,并跟板上PCIe Gen3 x8主接口通信。这是一张INVEA-TECH COMBO 80G HANIC的图:

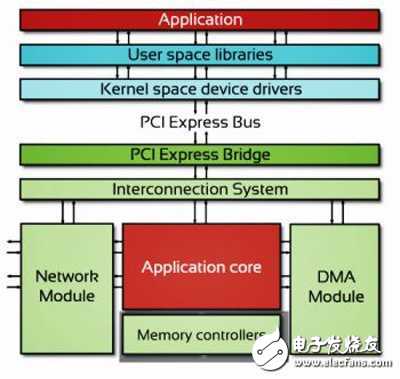

该公司的NetCOPE FPGA架构决定了使用这些基于FPGA的HANIC加速板能够快速开发网络应用。这个架构提供了一个独立于硬件的抽象层,它能快速处理重复性的开发任务,比如储存器控制、网络连接、主机通信,而且它还提供了一个对自定义应用内核的可配置的接口。使用NetCOPE架构开发的产品覆盖了不同的应用领域,比如VoIP分析、信息加密、HPC(高性能计算)、安全、生物信息学以及高速电子交易。

这是一张NetCOPE架构的通用的框图:

下面详细描述了这两块卡的区别:

INVEA-TECH COMBO 80G HANIC可以连接两个40Gbps QSFP+ 光纤(或者铜质)以太网收发器模块。一个板级的Virtex-7 690T FPGA用于接收以太网数据流,该FPGA通过4个工作在10Gbps的GTH 13.1Gbps SerDes来跟两个QFSP+模块通信。FPGA内部的可编程硬件逻辑用于处理以太网数据流中的数据包,并跟板上PCIe Gen3 x8主接口通信。这是一张INVEA-TECH COMBO 80G HANIC的图:

INVEA-TECH COMBO 80G hardware-accelerated NIC (HANIC)

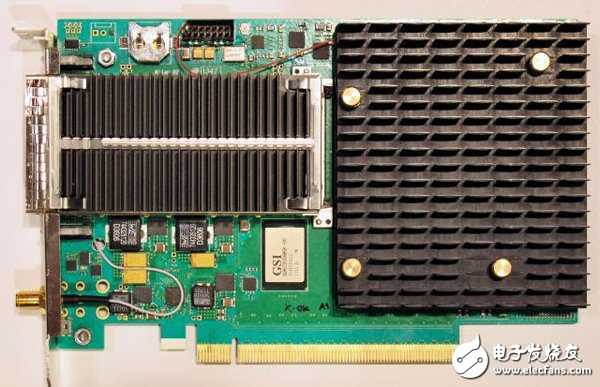

同样的,INVEA-TECH COMBO 100G HANIC与一个100Gbps CFP2光纤以太网收发器模块相连接,板级的Virtex-7 H580T 3D FPGA用于接收以太网数据流,该FPGA通过4个工作在25Gbps的GTZ 28.05Gbps SerDes来跟两个CFP2模块通信。更高的以太网传输速率需要使用一个PCIe Gen3 x16主接口来处理额外的流量带宽,下面是一张INVEA-TECH COMBO 100G HANIC板的图,通过比较上下两张图的PCIe连接器,你就可以看出区别。

INVEA-TECH COMBO 100G hardware-accelerated NIC (HANIC)

因为它们都是基于FPGA进行设计的,两块INVEA-TECH HANIC的板子都可以提供一些网络处理的选项,包括数据包采样,流量监控、数据包过滤、流量分析以及多个处理器核的流量分布。该公司的NetCOPE FPGA架构决定了使用这些基于FPGA的HANIC加速板能够快速开发网络应用。这个架构提供了一个独立于硬件的抽象层,它能快速处理重复性的开发任务,比如储存器控制、网络连接、主机通信,而且它还提供了一个对自定义应用内核的可配置的接口。使用NetCOPE架构开发的产品覆盖了不同的应用领域,比如VoIP分析、信息加密、HPC(高性能计算)、安全、生物信息学以及高速电子交易。

这是一张NetCOPE架构的通用的框图:

INVEA-TECH NetCOPE架构

(注:Xilinx今天宣布 Kintex UltraScale FPGA是第一个实现PCI Express规范的20nm器件,已经被列在PCI-SIG集成商列表中。UltraScale系列器件通过16Gbps GTH SerDes收发器来支持PCIe Gen3,每个器件中集成了2到6个PCIe模块)牛呀牛呀牛呀牛呀牛呀牛呀牛呀牛呀牛呀牛呀牛呀