例说FPGA连载77:FX2与FPGA之streamOUT模块代码解析

时间:10-02

整理:3721RD

点击:

例说FPGA连载77:FX2与FPGA之streamOUT模块代码解析

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

该模块的功能框图如图14.32所示。FX2读写状态机一旦检测到FX2的SlaveFIFO有可读取的数据,就进入FX2数据读取的状态,读取SlaveFIFO中所有的数据,缓存到片内RAM中。

图14.32 USB读写模块功能框图

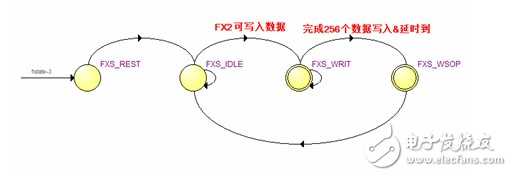

FX2读写状态机的状态迁移如图14.33所示。上电状态为FXS_REST ,随后就进入FXS_IDLE状态,判断SlaveFIFO是否有可读取数据,若有则进入FXS_READ状态读出FX2的SlaveFIFO中所有的数据,接着进入FXS_RSOP状态停留一个时钟周期,最后回到FXS_IDLE状态,如此反复。

图14.33 USB读写模块状态转移图