以太网图像传输验证系统-结项报告

为期两月的Artix-7 50T开发板评测转瞬即逝,在此期间笔者对开发板进行了一定的了解,可查看以下博文:

【Artix-7 50T FPGA试用体验】一 初上手

首先根据官方向导,按部就班的上手板子,板载程序的测试;然后开始搭建软件,安装vivado开发软件,安装板子JTAG、USB-TO-UART驱动,为开发做好了一切准备。

随后细谈板子上的硬件资源,包括电源、时钟、Artix-7 50T外设资源等,如下几篇博文:

【Artix-7 50T FPGA试用体验】二 板卡细探(一)

【Artix-7 50T FPGA试用体验】二 板卡细探(二)

一切就绪,开始上手FPGA调试和开发了,

第一步,对以太网接口做了深入调试,包括物理层的调试,如下博文:

【Artix-7 50T FPGA试用体验】以太网接口调试

然后在协议栈层对以太网进行了调试开发:

【Artix-7 50T FPGA试用体验】四 LwIP以太网调试

第二步,对DDR3 SDRAM进行了研究,对其在xilinx FPGA中的接口做了调试,而且做了上板测试:

【Artix-7 50T FPGA试用体验】DDR3调试

此篇结项报告,融合一下之前的成果,笔者准备了小的测试项目,结构如下图:

1. 由PC端发送以太网数据,经过板载PHY接收,输入到FPGA中

2. FPGA中通过RMIIRX接口接收数据,然后写入DDR3 SDRAM中

3. 一帧以太网数据写入DDR3 SDRAM后,开发读取,送入RMII TX接口模块

4. PHY收到RMIITX输出数据,数据又回传到PC端

此小项目实现了一个loopback的功能,数据经过了以太网PHY,DDR3两个外设,FPGA中只是对数据进行了透传。

硬件连接图如下:

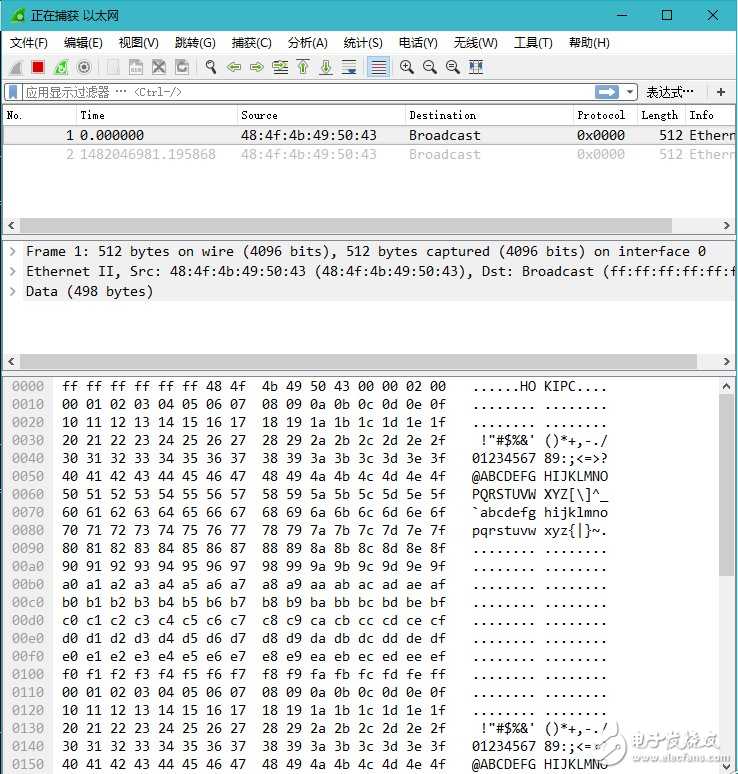

PC端发送512字节的一帧以太网数据

通过wireshark抓取到了两帧数据,一帧是发送的数据,另一帧是回传的数据,两帧的数据完全相同

至此,Artix-7 50T的先期试用报告完结,下一步笔者会继续项目,分享更多的评测博文

写的非常到位 了解一下

厉害,,,,,,,