摄像头接口测试

时间:10-02

整理:3721RD

点击:

1. 本次使用的摄像头为 淘宝买的模块。美光的CMOS摄像头MT9D111。这个芯片用起来不是很难。所有的处理功能、内存以及与镜头的接口都集成在一个单传感器处理芯片上。应该是SOC之类。

2. 引脚图如下:有一个I2C总线,同步时钟,场和行的同步信号,一个8位的并行数据口。

3. 我们首先需要初始化1个ROM区域,以后会用到,一般在ALTERA器件里面,我之前用过Mif格式的文件用来保存一张图片的信息。记得以前用的时候,需要先把gif文件用C++程序生成 mif 文件。其实mif不太好写,尤其数据量大的时候。

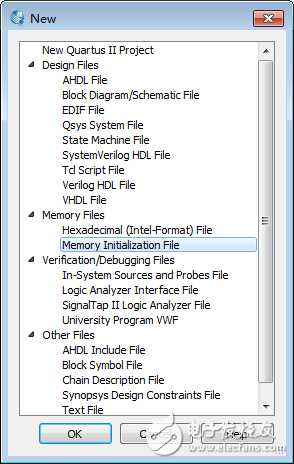

初始化需要quartus 工具。新建文件 内存初始化文件

按照基本的流程创建完毕。

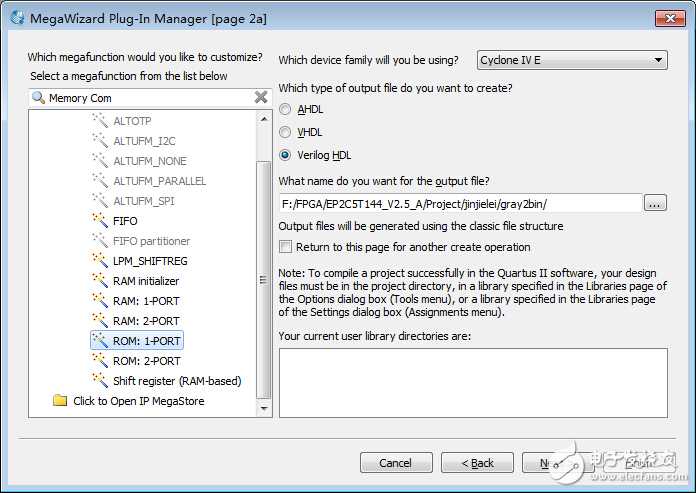

4. 接下来需要配置个IP核 ,这个IP核用来管理ROM。在tool- megawizard plug in manager 里面

找到我们需要用到的IP核

然后在接下来的步骤中找到 “mem init‘’选项找到我们刚才创建的mif文件。

到summery界面,找到我们的 v文件,把这个例化文件拷贝到我们的例程。

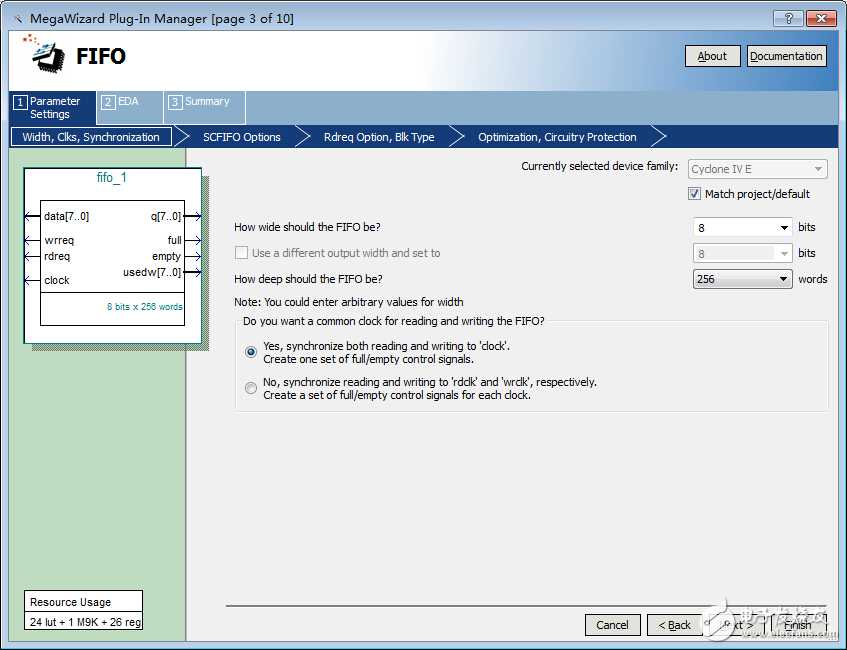

5. FIFO配置

本次需要创建3个 FIFO,video 使用的(视频时域变换),DDR内存使用的,读写SDRAM使用的。

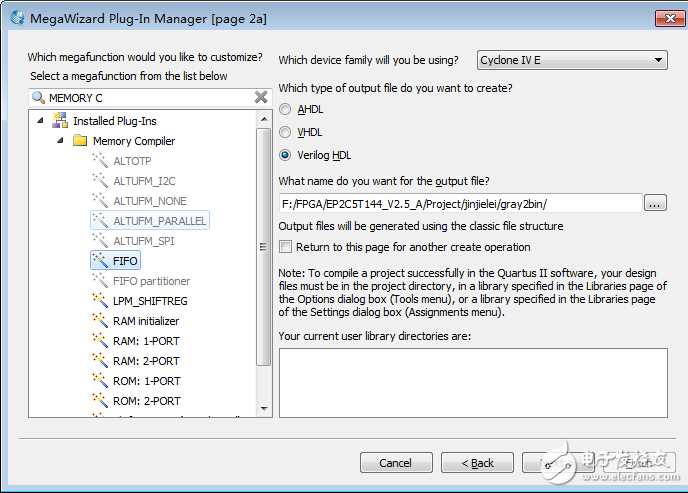

创建FIFO用到quqrtus工具。

video 使用的(视频时域变换) 注意下面和之前的IP核创建一样的,只是这次选的是FIFO。

接下来选择FIFO的深度和宽度,深度512,宽度8,就是这个FIFO可以存储 512个字节的数据。剩下2个FIFO基本一样配置。

6. 我们这次代码主要是摄像头部分,接口有I2C接口,8位并口

由于代码比较多,主要说下接口定义,关于内部实现可能篇幅太大了。

下面是I2C接口的部分。

//MAX9526低功耗视频解码器将NTSC或PAL复合视频信号转换成8位或10位YCbCr分量视频

module iic_ctrl(

clk,rst_n,

tiic_en,tiic_ab,tiic_db,

scl,sda

);

input clk; // 50MHz主时钟

input rst_n; //低电平复位信号

input tiic_en; //需要通过IIC接口配置MAX9526使能信号,高电平有效

input[7:0] tiic_ab; //需要通过IIC接口配置MAX9526地址

input[15:0] tiic_db; //需要通过IIC接口配置MAX9526数据

output scl; //串行配置IIC时钟信号

inout sda; //串行配置IIC数据信号

//下面是8位并口的数据

module video_ctrl(

clk,rst_n,

vpclk,vvsync,vhref,vdb,

wrf_din,wrf_wrreq

);

input clk; //系统时钟,25MHz

input rst_n; //复位信号,低电平有效

//视频输入接口

input vpclk; //视频时钟

input vvsync; //视频场同步信号

input vhref; //视频行同步信号

input[7:0] vdb; //视频数据总线

//wrFIFO输入控制接口

output[15:0] wrf_din; //sdram数据写入缓存FIFO输入数据总线

output wrf_wrreq; //sdram数据写入缓存FIFO数据输入请求,高有效

7. 摄像头数据保存在哪里? 读到的数据会暂时保存在这个队列里面缓冲,然后再把数据全部写到SDRAM里面。

video_fifo uut_videofifo(

.aclr(v_clr),

.data(vdb),

.rdclk(clk),

.rdreq(vf_rdreq),

.wrclk(vpclk),

.wrreq(vhref),

.q({wrf_din[7:0],wrf_din[15:8]}), //input first--LSB,input second--MSB

.rdusedw(vf_rduse)

);

8. 总结,本次很多参考了特权的资料,因为我以前也没搞过,借此机会学习一下。

目前我只有摄像头,只是把摄像头数据可以保存下来,通过quartus工具查看有没有数据,因为目前还没接LCD,这 是下一步的计划。

这次收获很大,流程搞懂,代码也熟悉起来了。有时间我会把怎么查看数据截下图。

话说你这样创建的文件,怎么往xilinx的vivado上移植。

我就不懂了,你quartus 和XILINX也能搞在一起。唬人的吧