第一次使用quartus prime,仿真时钟问题

时间:10-02

整理:3721RD

点击:

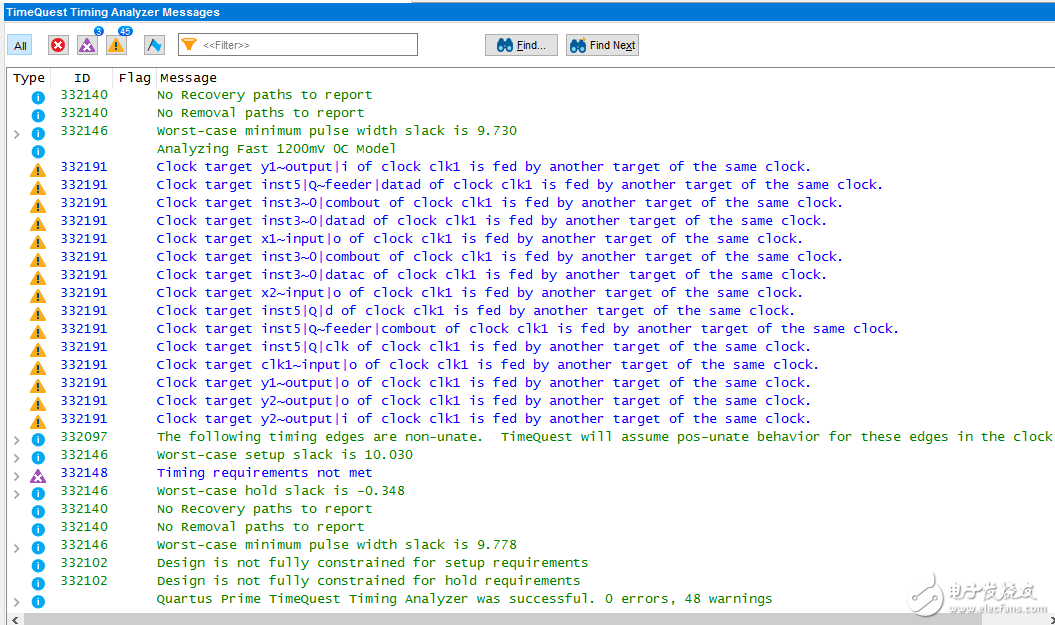

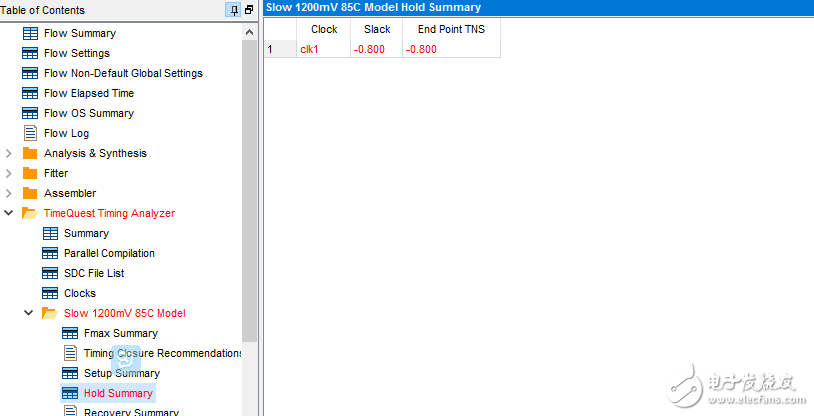

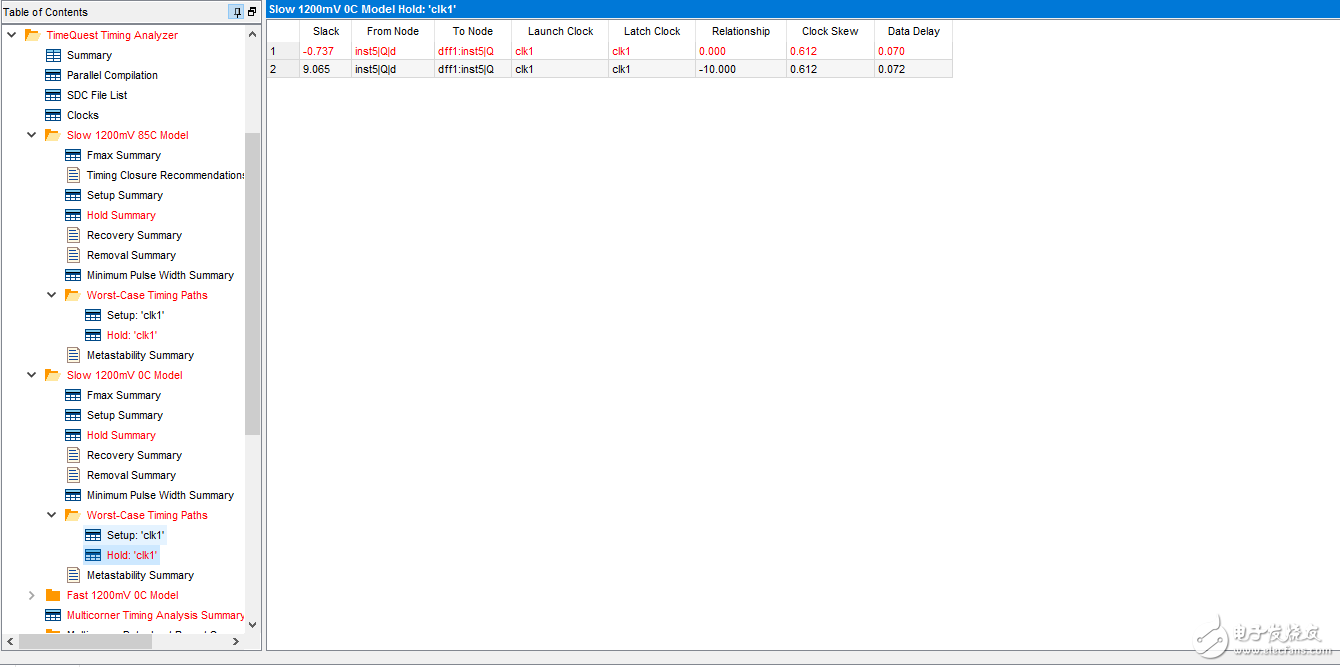

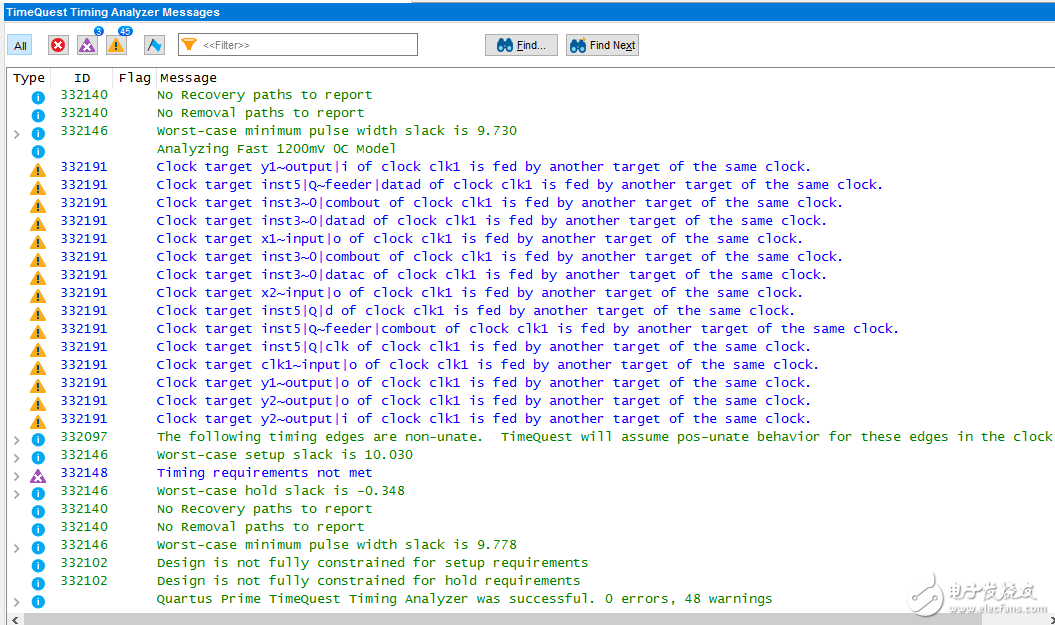

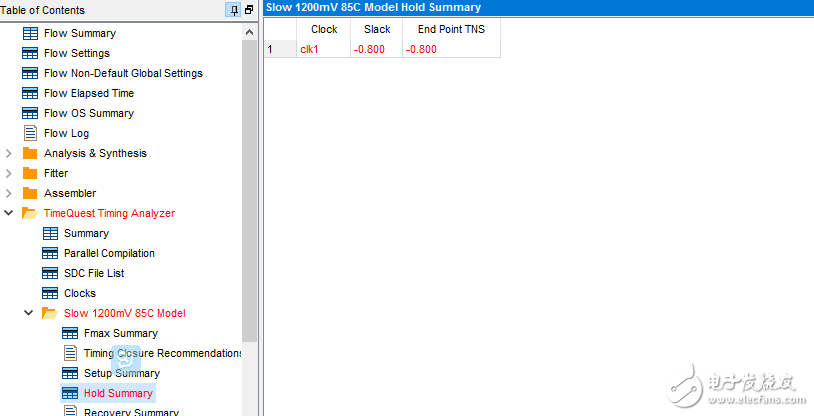

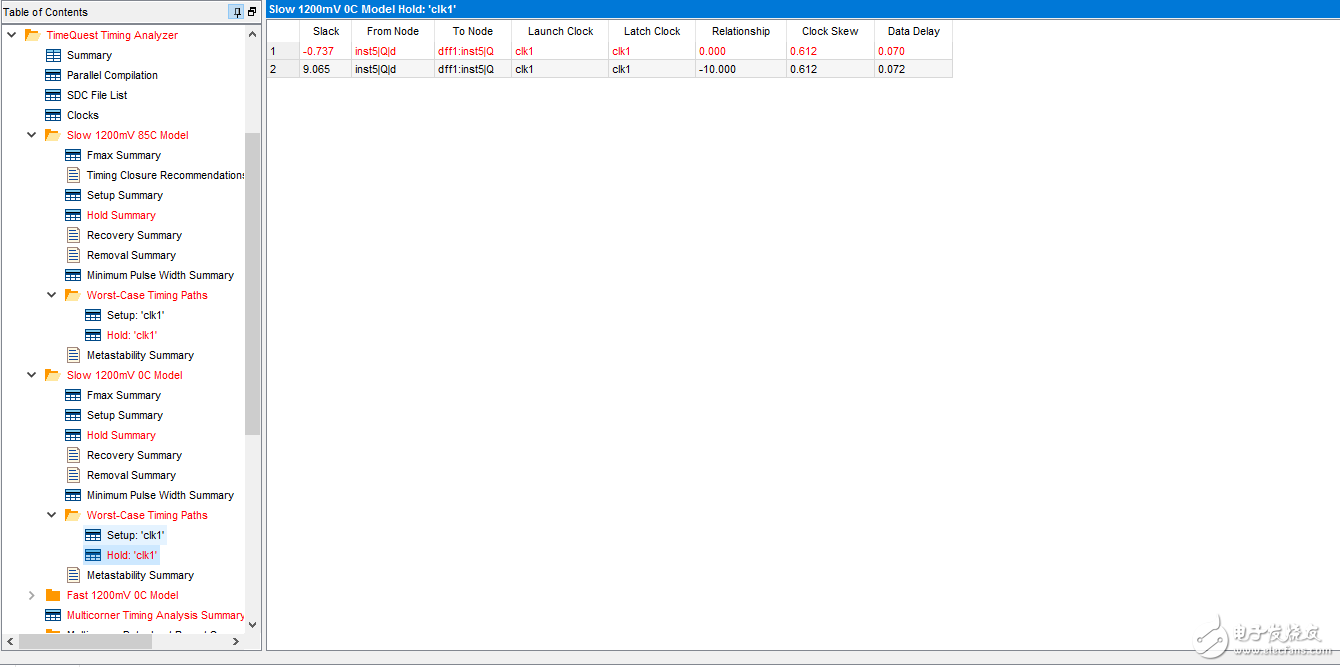

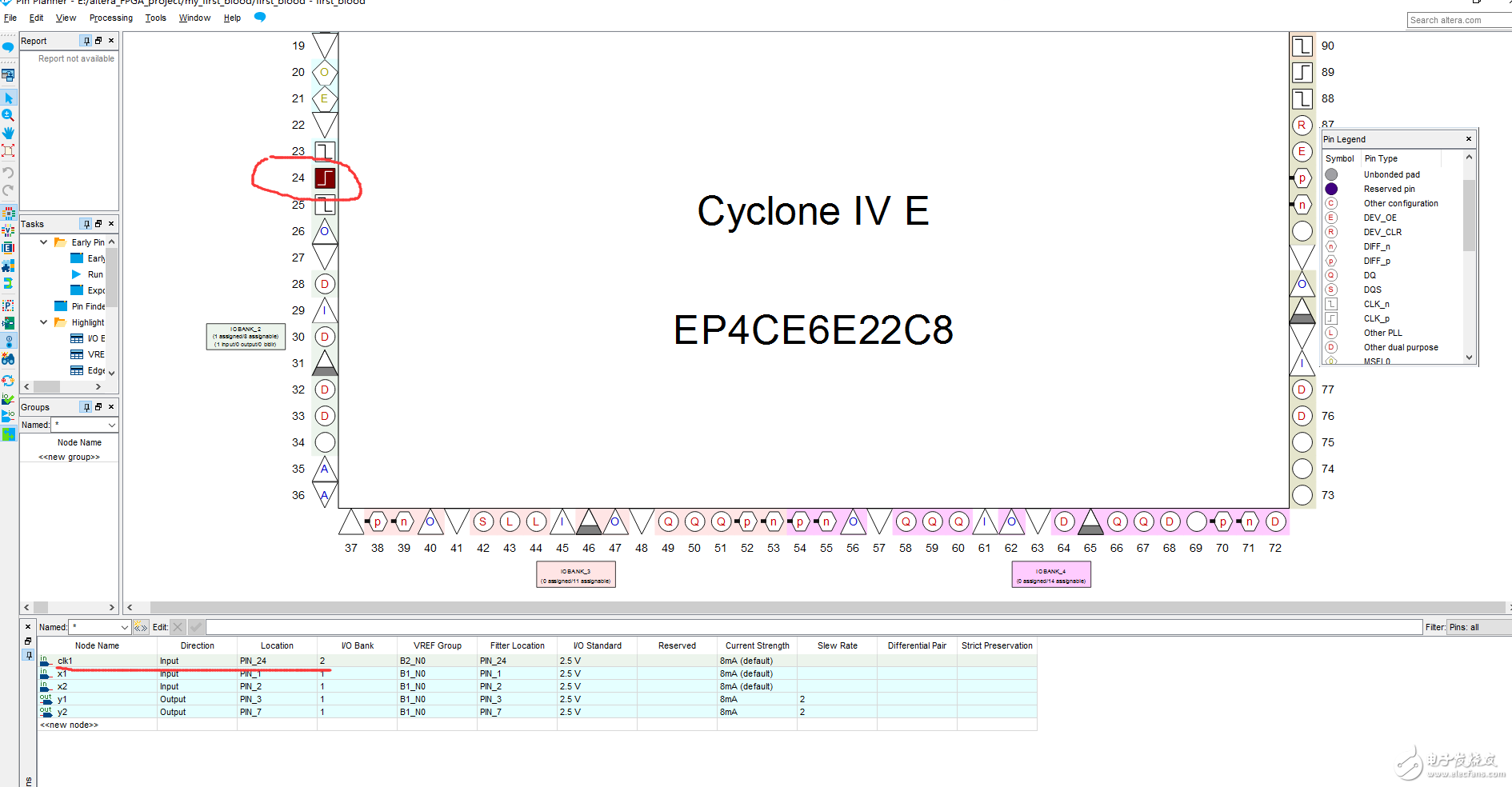

初学fpga,在仿真时遇到的问题,使用的教材是老板quartus II的,结果总是提示时钟输出有问题,报错如图

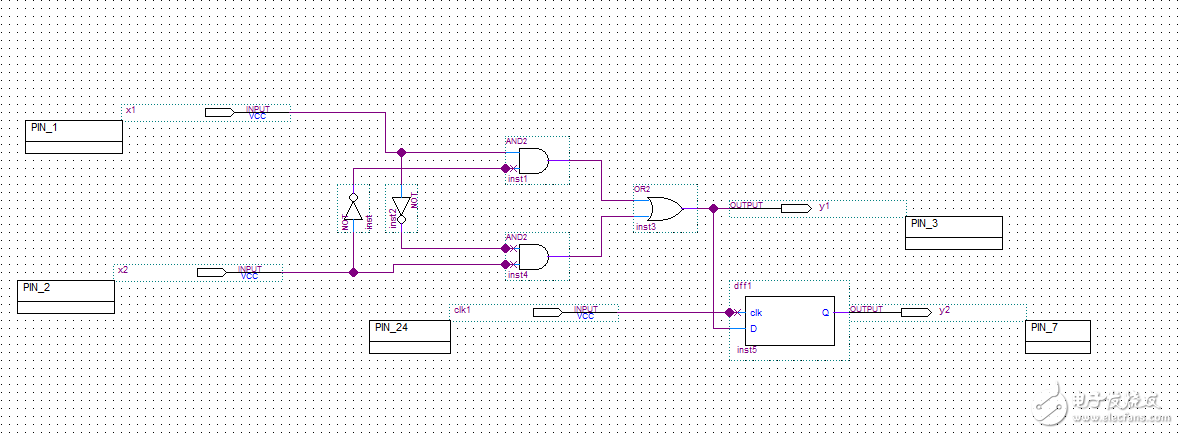

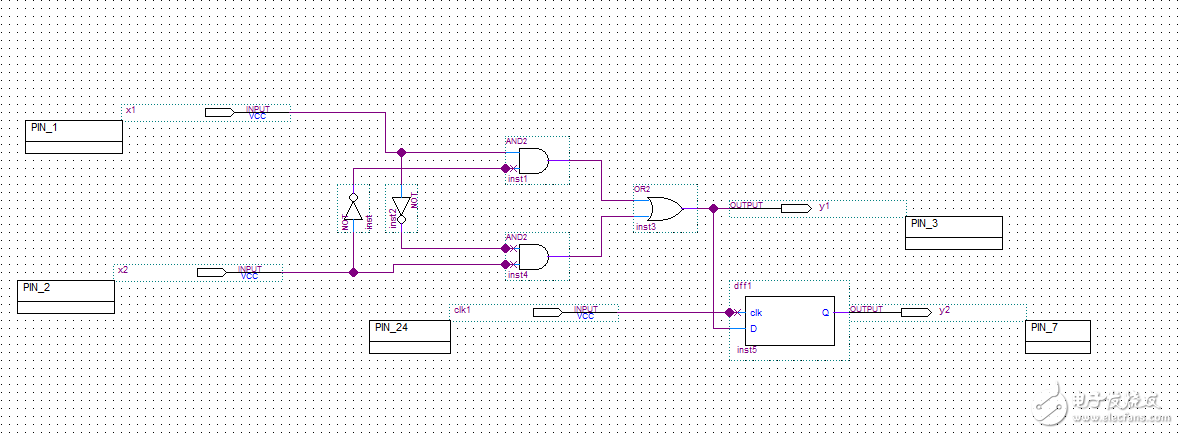

bdf图:

其中clk是时钟输出口,我从pin

其中clk是时钟输出口,我从pin

planer里面找的时钟端,不知道这么设置对不对,求指教出错的地方

而且报错的逻辑口除了有时钟输入的D触发器还有或门,输入口和输出口,所以我就不知道出错的地方在哪了

bdf图:

其中clk是时钟输出口,我从pin

其中clk是时钟输出口,我从pin planer里面找的时钟端,不知道这么设置对不对,求指教出错的地方

哦哦,你那是用的原理图输入设计。多看看别的教材吧,那种方法无法进行大规模开发,大工程总不能画一个好几百个与非门的原理图吧?学学verilog,或者vhdl语言开发才是主流。

小编出现的警告是:那几个输入输出逻辑,本来是想用clk1驱动,但是它们已经被另外一个时钟给驱动了。问题可能出在几点:1查看你Verilog/VHDL代码,是不是多写了一个时钟,2查看pin planned是不是时钟管脚用错了。最好把代码发出来看看有没有问题。

因为是第一次写所以抄的是例程

代码如下:

module dff1(clk,D,Q);

output Q;

input clk,D;

reg Q;

always @(posedge clk)

Q <= D;

endmodule

时钟clk1用的也是片子上的时钟输入口

而且报错的逻辑口除了有时钟输入的D触发器还有或门,输入口和输出口,所以我就不知道出错的地方在哪了

跟你发的图管脚名字都不一样,确定是一个代码吗?你的代码里,定义了一个输出叫D,时钟上升沿来了,D什么都没干。你抄的例程有问题吧。初学的话,最好先买个开发板,用配套的例程,随便找教材看容易进坑

昨晚在手机上看的没显示全部内容。你的代码仅仅是一个D触发器的代码。整体硬件电路描述的代码呢?你是不是用的图形输入模式直接搭出来的?

嗯,是的,用verilog写器件然后生成图形加入到bdf图里去的,那些非门与门或门都是quartus自带的库,难道不是这样做么。