IP核之ROM(四)SignalTap II仿真

时间:10-02

整理:3721RD

点击:

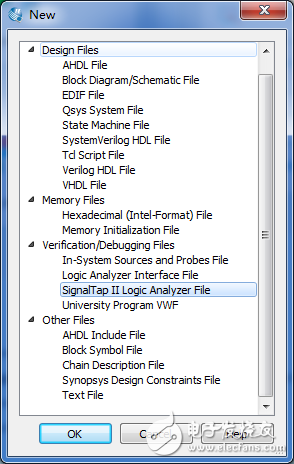

新建SignalTap II 调试文件。

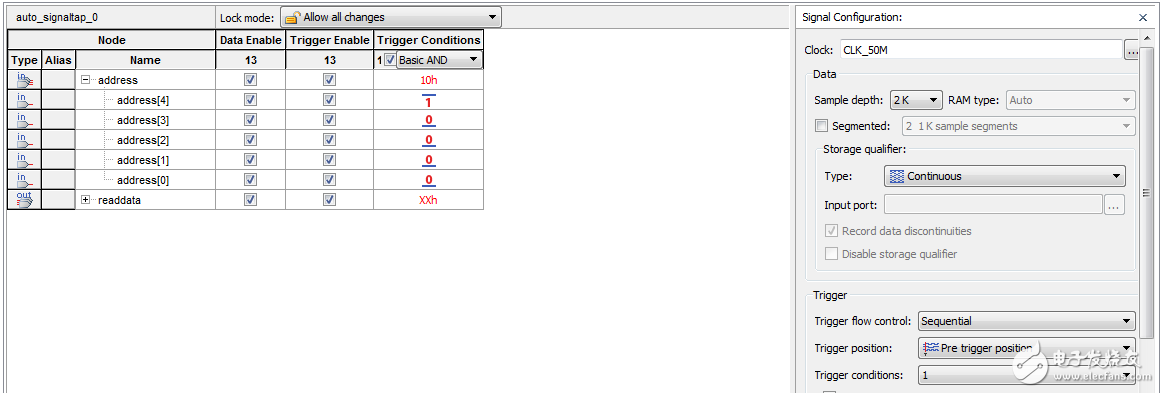

添加address与readdata.

将address设置为10h触发,采样时钟为CLK_50M,采样深度为2K。

设置好后,重新编译一次工程,将程序下载到开发板上,按下第5个按键,这时D5的LED灭了,程序触发后得到如下的波形,相应的数据也是0x10了。

真的很不错的哦要好好学习了