IP核之ROM(三)ModelSim仿真

时间:10-02

整理:3721RD

点击:

下面简述一下过程。

在 Tools --> Options 中检查 ModelSim的路径,要加一个“\”,前面已经提过了原因。

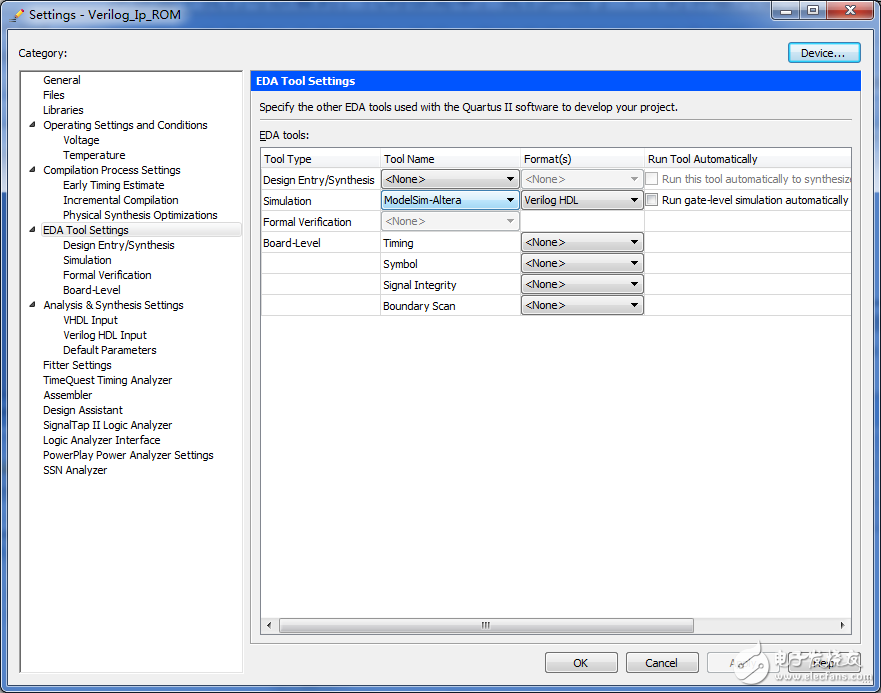

在Assignments --> Settings -->EDA Tool Settings中设置仿真软件为ModelSim-Altera ,语言为Verilog HDL。

在Processing --> Start -->Start TestBench Template Writer,生成TestBench模板。

打开My_ROM.vt文件,进行修改。

- `timescale 1 ps/ 1 ps

- module Verilog_Ip_ROM_vlg_tst();

- // constants

- // general purpose registers

- reg eachvec;

- // test vector input registers

- reg CLK_50M;

- reg RST_N;

- reg [4:0] address;

- reg [4:0] address_n;

- // wires

- wire [7:0] readdata;

- // assign statements (if any)

- Verilog_Ip_ROM i1 (

- // port map - connection between master ports and signals/registers

- .CLK_50M(CLK_50M),

- .RST_N(RST_N),

- .address(address),

- .readdata(readdata)

- );

- initial

- begin

- CLK_50M = 0;

- RST_N = 0;

- #10 RST_N = 1;

- #1000000 $stop;

- end

- always #10000 CLK_50M = ~CLK_50M;

- always @ (negedge CLK_50M or negedge RST_N)

- begin

- if(!RST_N)

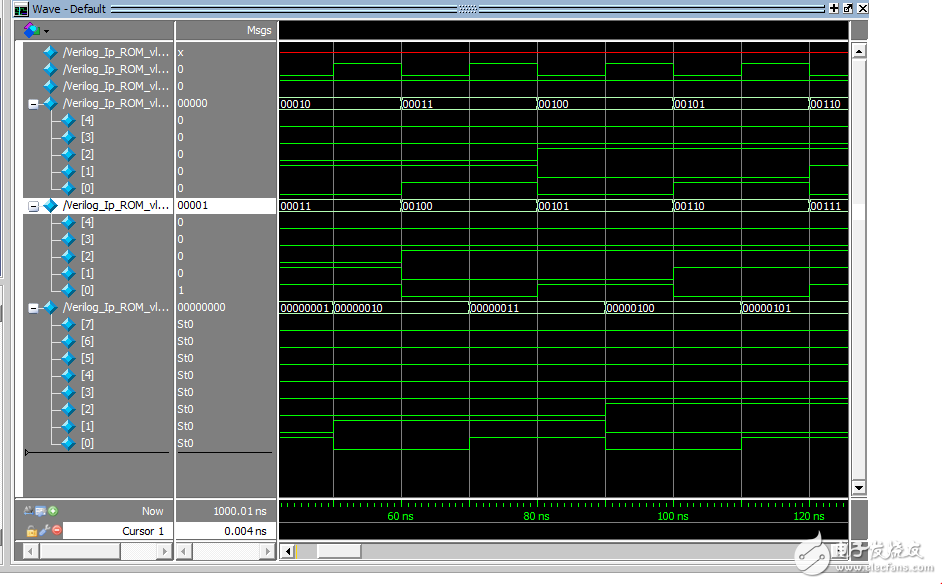

- address Run Simulation Tool-- > RTL Simulation

可以看到,数据的读取在第0ns时就读取,这是由于在配置ROM IP核时的Regs/Clken/Aclrs页面把q outputport.设置去掉了。