quartus ii 时序仿真出现了问题

时间:10-02

整理:3721RD

点击:

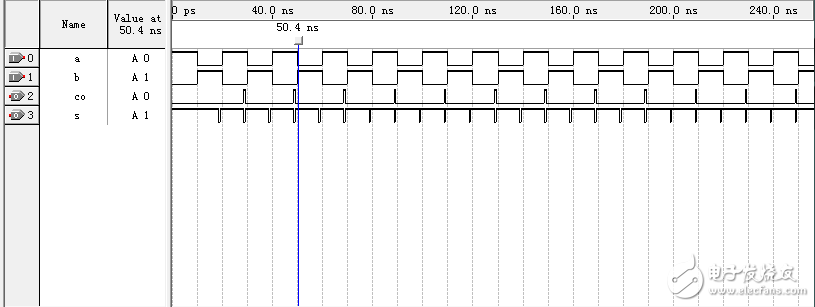

两个输入管脚分别输入了一个时钟信号,而且两个信号是反相的。输出之后来应该是输出端s位高电平,co为低电平才对的,但是输出出现了一些峰刺还是什么的。用功能仿真就没有这个问题。请大家帮我分析一下。谢谢

简单的半加器

你的RTL级别仿真有毛刺吗,如果只有时序仿真有,说明你这是由于组合逻辑引起的毛刺。就是说你a,b两条时序,实际电路中达到上升下降沿不是同时的,所以输出的s、co两条线就会跳变出毛刺。最好的解决方法是再加一路时钟CLK,当CLK出现上升或下降沿的时候,进行一次a、b的组合逻辑判断

有大神评论一下吗?

冒险竞争!

听说过,能分析一下上面的时序吗?

就是说a,b的跳变沿并不在同一个时刻,导致出现a=1,b=1或者a=0,b=0的情况

quartusII的时序仿真是综合布局布线后的仿真。仿真里面含有各种门延时和布线延时,会如实地反应出逻辑电平的冒险竞争现象。

功能仿真则不会有此毛刺,这是因为功能仿真没有考虑各种延时,而只是单纯地对代码的逻辑行为进行仿真。

贴出代码看看,c0应该是组合逻辑实现的吧?