移位寄存器Shift Register(RAM-based)的如何实现延时

时间:10-02

整理:3721RD

点击:

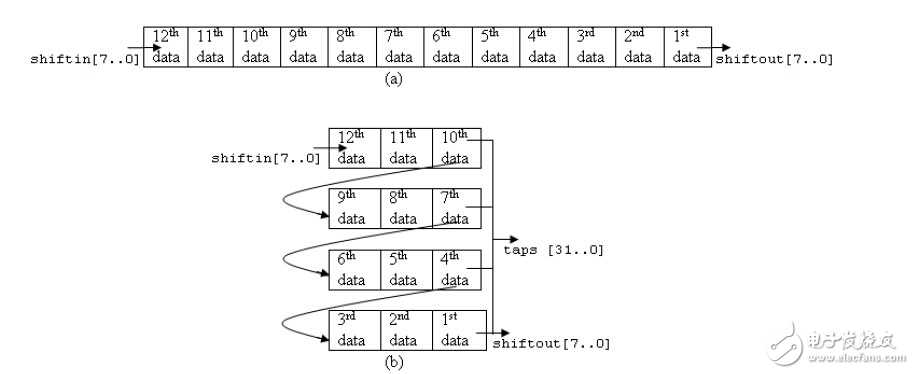

想请问大家,移位寄存器Shift Register(RAM-based)的如何实现延时,也看了一些关于IP核的资料,可是还是不是很明白,看到下面这个图的例子,我只知道抽头是4,distance是3,貌似延时就是用4*3=12个时钟,可是我不是很理解,传统的移位寄存器和这种基于RAM究竟区别在哪里呢,我觉得都是从shiftout输出啊,真的不太明白,希望大牛们赐教,能写下分析过程,谢谢大家了。

基于RAM的移位寄存器可以输出shiftout[7..0],跟输入位宽一样。也可以输出taps[31:0],抽头就是输出位置,可以并行的输出1,4,7,10这个4个数,下一个时钟并行输出2,5,8,11这四个数,位宽=抽头数*输入数据位宽。

恩恩,谢谢了,问题已经解决了。

高手啊,回答的真好