例说FPGA连载32:PLL例化配置与LED之使用Pin Planner进行引脚分配

时间:10-02

整理:3721RD

点击:

例说FPGA连载32:PLL例化配置与LED之使用Pin Planner进行引脚分配

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

如图3.18所示,点击菜单栏“AssignmentsàPin Planner”。

图3.18 菜单选择Pin Planner

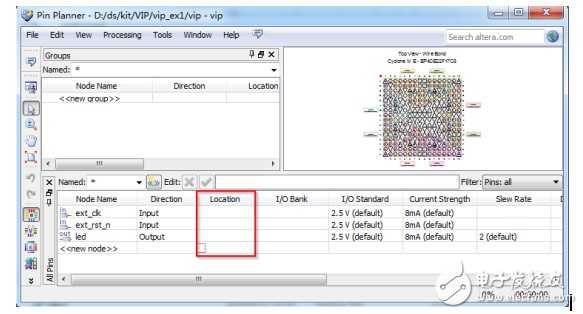

在弹出的“Pin Planner”中,找到如图3.19所示的“All Pins”选项卡。“Node Name”罗列了所有在设计工程的顶层代码中申明过的引脚信号,我们找到它们所对应的“Location”列,这里可以输入或者查找相应的引脚进行分配。

图3.19 Pin Planner界面

如图3.20所示,我们给ext_clk对应的Location列输入了引脚号“E15”。这就完成了ext_clk信号的引脚分配。

图3.20 Pin Planner引脚分配

引脚分配是基于什么?拍拍脑袋,随心所欲?非也,引脚的分配一定是有理有据,那就是我们已经设计好的硬件原理图。如图3.21所示,这里FPGA所使用的时钟信号ext_clk对应原理图上的网络名CLK_25M,它的FPGA引脚号是E15,那么我们就给它分配E15。

图3.21 时钟信号的引脚连接原理图