求教 关于FPGA进行采样时,时钟与数据不同步的问题。

时间:10-02

整理:3721RD

点击:

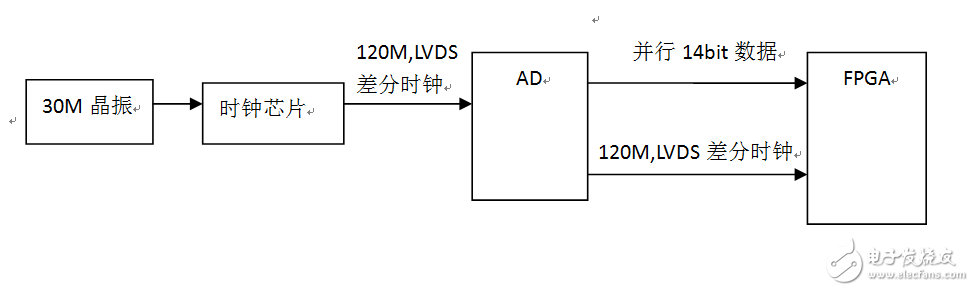

上图是我的系统结构,FPGA使用AD产生的120M差分时钟作为时钟,通过一个DCM生成120M,240M的时钟,使用DCM生成的时钟作为AD采样时钟来采样并行14bit差分数据。每次修改了FPGA的代码时,都需要调整采样时钟的相位才能够进行正确的采样,有时调整相位也采样不正确。这是采样时钟与数据不同步造成的么?

我在网上看了一些资料,说可以使用idelay增加时钟的延时,我的FPGA使用的是spartan6的lx150,ISE版本为14.4。我在使用selectIO这个IP核时,怎样才能只改变时钟的延时,不改变数据延时呢?是把IP核设置里的data delay设置为0,clock delay设置为自己想要的延时么?但是这样设置完成以后,生成的模块仍然会有数据的输入引脚,和输出引脚,这些引脚怎么办呢?我只想要时钟延时。

还有没有其他的方法来解决同步这个问题呢?

DCM是锁相环吧,为啥要用锁相环输出的时钟采数,经过锁相环的时钟已经不是同源时钟了,相位有偏差,直接用输入的120M时钟采数,如果要跨到240M时钟用fifo跨,切记要同源!还有一点,输入端可以用一个ddio,保证延时最小!