关于RTL仿真和门级仿真求助~

时间:10-02

整理:3721RD

点击:

刚刚本科毕业,假期导师要求做一个设计。实验室没有做过FPGA的学长只好问网上的各位了。

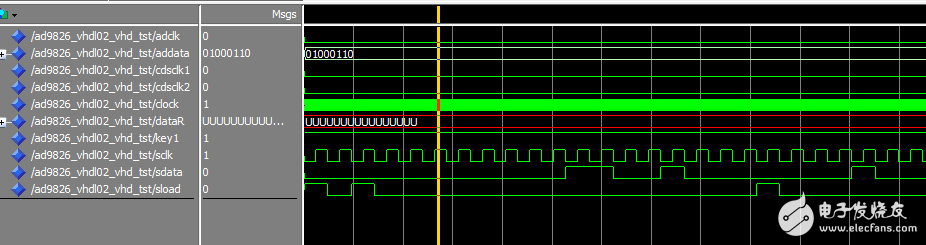

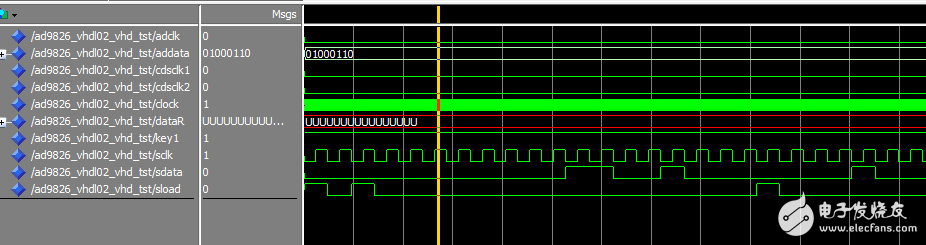

写好的FPGA代码进行RTL仿真波形是符合要求的,如下图。

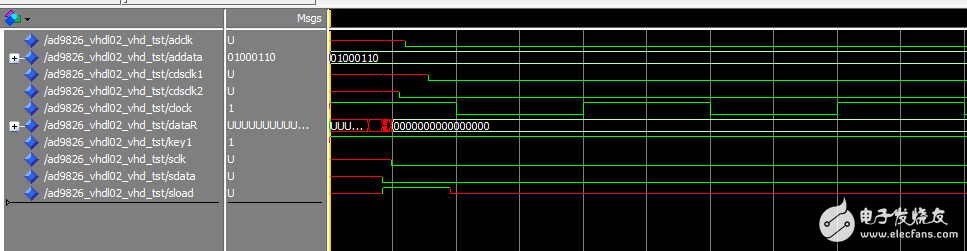

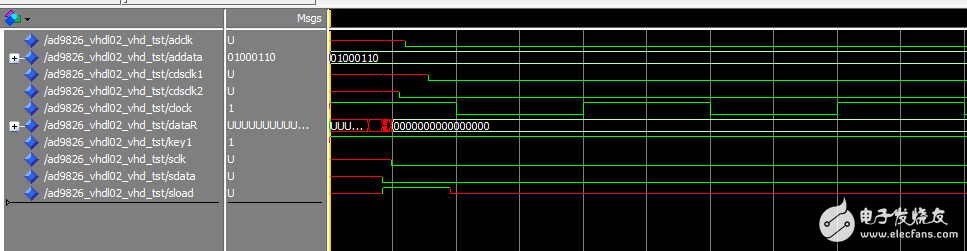

但是做门级仿真的时候,时序就不对了,变成了这样。

第一次做不太懂,求大家告诉我,可能是哪里出问题了?做完行为级仿真以后还需要做什么才能保证门级仿真通过?谢过大家了。

写好的FPGA代码进行RTL仿真波形是符合要求的,如下图。

但是做门级仿真的时候,时序就不对了,变成了这样。

第一次做不太懂,求大家告诉我,可能是哪里出问题了?做完行为级仿真以后还需要做什么才能保证门级仿真通过?谢过大家了。

不懂 但是为了能让小编获得帮助 也只能顶贴了

FPGA是用什么仿真的啊?

不是太清楚哎!

建议把 testbench里面那个 'timescal 1ps/1ps 精度改为1ns/1ps,或者看看你testbench文件的时钟频率是否与quartus的时钟一致。

竟然又是ad。看得我心碎

用的是ModelSim

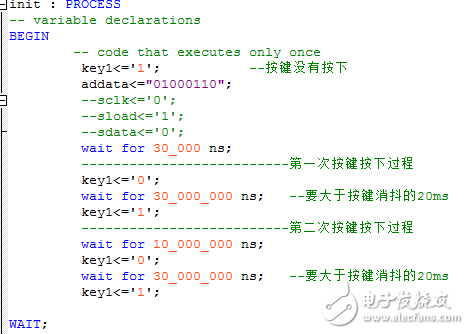

自问自答了。问题已经解决。开始一直认为是timequest的时序约束没有做好,后来证明和时序约束一点关系都没有。两个原因1.代码中的初值和后面时序逻辑冲突了,所以一开始的值是x,2Testbench中如果要对几个引脚初始化的话,最好不要在PROCESS中初始化。因为很可能与自己在别处又初始化了,数值各种冲突。比如说我在附图中注释掉的那三局就是问题所在。

刚开始学FPGA,各种碰壁,现在开始解决仿真波形里面的毛刺问题了,跪谢叔叔阿姨的帮助,祝大家愉快。

Testbench代码

门级仿真用的什么软件啊?也是modelsim?

您好,想请教小编一个问题,您用VHDL时使用过SLL这个操作运算没,要是用过的话是怎么使用的呢?

自学每人请教确实需要自己苦学阿

是的,在quartus的tool菜单里的Gate level simulation

没用过移位操作,刚学了没俩月

利用modelsim仿真为功能仿真(不带有时延信息),只能验证你的代码的逻辑性,而要对其进行功能仿真时一定要保证测试文件的正确性,给的激励一定要对。功能仿真之后可以下到fpga当中,实际的检测你的代码产生的时序是否符合要求。