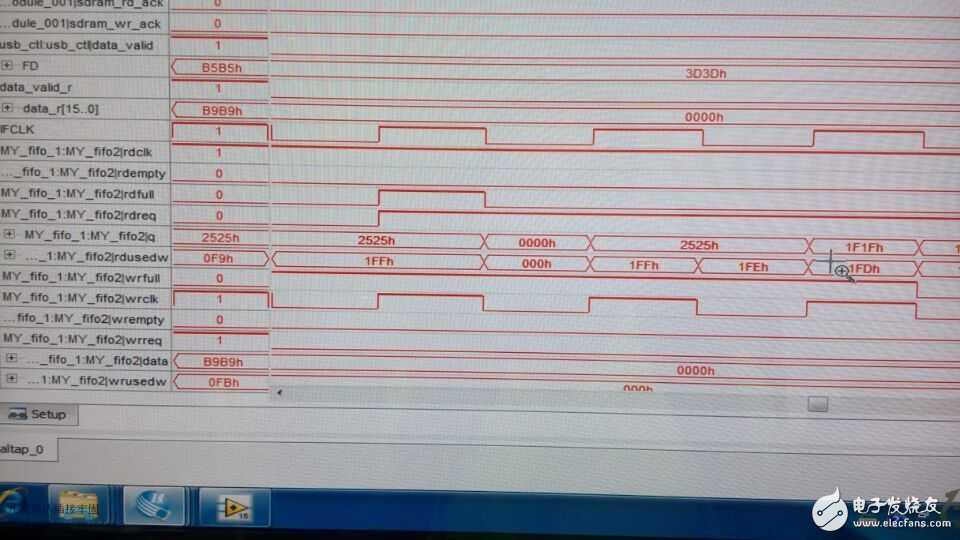

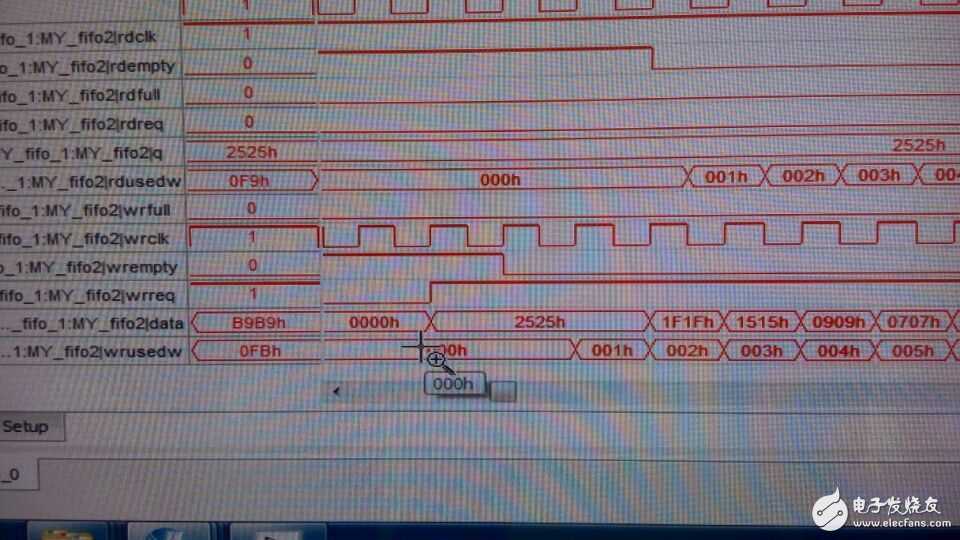

fifo读写问题

无论怎么写数据,fifo读出来的第一个数怎么都是0

谢谢了小编,好东西大家一起来分享!

是不是延时了一拍

看不是很清楚

专业FPGA设计,有需求请联系QQ827492034

仿真看看,这样看没懂~~~

程序问题,程序拿出来

如果FIFO是IPCore,确定一下读延时,也就是看看读数据有没有被寄存后输出,这样就会多一个周期。

当CPU在某一时段来不及响应所有的指令时,指令就会被安排在FIFO队列中,比如0号指令先进入队列,接着是1号指令、2号指令……当CPU完成当前指令以后就会从队列中取出0号指令先行执行,此时1号指令就会接替0号指令的位置,同样,2号指令、3号指令……都会向前挪一个位置.

FIFO是队列机制中最简单的,每个接口上都存在FIFO队列,表面上看FIFO队列并没有提供什么QoS(Quality of Service,服务质量)保证,甚至很多人认为FIFO严格意义上不算做一种队列技术,实则不然,FIFO是其它队列的基础,FIFO也会影响到衡量QoS的关键指标:报文的丢弃、延时、抖动。既然只有一个队列,自然不需要考虑如何对报文进行复杂的流量分类,也不用考虑下一个报文怎么拿、拿多少的问题,而且因为按顺序取报文,FIFO无需对报文重新排序。

FIFO的深度,THE DEEPTH,FIFO可以存储多少个N位的数据(如果宽度为N)。如一个8位的FIFO,若深度为8,它可以存储8个8位的数据,深度为12 ,就可以存储12个8位的数据,FIFO的深度可大可小。在FIFO实际工作中,数据的满/空标志可以控制数据的继续写入或读出。

FIFO设计的难点在于怎样判断FIFO的空/满状态。为了保证数据正确的写入或读出,而不发生溢出或读空的状态出现,必须保证FIFO在满的情况下,不能进行写操作。在空的状态下不能进行读操作。

谢谢分享,好东西大家一起来分享!

一般IP核都会延时一个周期 ,你试试写入的数据及其初始化值为非0数