cyclone V控制DDR3的读写,quartusII配置DDR3 ip核后,如何调用实现DDR3的读写呢,谢谢

没有用过Altera的芯片,只用过Xilinx的。但是原理应该差不多。所谓DDR3 IP核,实际上是DDR3控制器。这个控制器的接口有两类,一类面向用户,另一类直接连到DDR3芯片。它起什么作用呢?实际上就是简化DDR3的读写时序(因为直接实现DDR3读写时序太复杂了)。用户只要通过操作控制器的用户接口,就可以实现DDR3的读写操作了。控制器可以自动完成DDR3的初始化,并根据用户接口产生DDR3的读写时序,自动产生小编说的RASn,CASn,WE, DQ这些信号,从而实现DDR3的读写。一般配置完IP后,在该IP目录下会生成仿真文件,可以通过运行这个现成的仿真文件来熟悉DDR3 IP的使用。另外要有看user_guide的习惯,user_guide里会介绍IP的使用方法。

楼上的写得很好!让我明白了IP的作用!向你学习!还有什么相关资料吗

谢谢您的回答。您说的IP控制器产生的两类接口,altera的DDR3 ip产生的文件中生成的接口如下:

module ddr3ip (

input wire pll_ref_clk, // pll_ref_clk.clk

input wire global_reset_n, // global_reset.reset_n

input wire soft_reset_n, // soft_reset.reset_n

output wire afi_clk, // afi_clk.clk

output wire afi_half_clk, // afi_half_clk.clk

output wire afi_reset_n, // afi_reset.reset_n

output wire afi_reset_export_n, // afi_reset_export.reset_n

output wire [14:0] mem_a, // memory.mem_a

output wire [2:0] mem_ba, // .mem_ba

output wire [0:0] mem_ck, // .mem_ck

output wire [0:0] mem_ck_n, // .mem_ck_n

output wire [0:0] mem_cke, // .mem_cke

output wire [0:0] mem_cs_n, // .mem_cs_n

output wire [1:0] mem_dm, // .mem_dm

output wire [0:0] mem_ras_n, // .mem_ras_n

output wire [0:0] mem_cas_n, // .mem_cas_n

output wire [0:0] mem_we_n, // .mem_we_n

output wire mem_reset_n, // .mem_reset_n

inout wire [15:0] mem_dq, // .mem_dq

inout wire [1:0] mem_dqs, // .mem_dqs

inout wire [1:0] mem_dqs_n, // .mem_dqs_n

output wire [0:0] mem_odt, // .mem_odt

output wire avl_ready, // avl.waitrequest_n

input wire avl_burstbegin, // .beginbursttransfer

input wire [25:0] avl_addr, // .address

output wire avl_rdata_valid, // .readdatavalid

output wire [63:0] avl_rdata, // .readdata

input wire [63:0] avl_wdata, // .writedata

input wire [7:0] avl_be, // .byteenable

input wire avl_read_req, // .read

input wire avl_write_req, // .write

input wire [2:0] avl_size, // .burstcount

output wire local_init_done, // status.local_init_done

output wire local_cal_success, // .local_cal_success

output wire local_cal_fail, // .local_cal_fail

input wire oct_rzqin, // oct.rzqin

output wire pll_mem_clk, // pll_sharing.pll_mem_clk

output wire pll_write_clk, // .pll_write_clk

output wire pll_locked, // .pll_locked

output wire pll_write_clk_pre_phy_clk, // .pll_write_clk_pre_phy_clk

output wire pll_addr_cmd_clk, // .pll_addr_cmd_clk

output wire pll_avl_clk, // .pll_avl_clk

output wire pll_config_clk, // .pll_config_clk

output wire pll_mem_phy_clk, // .pll_mem_phy_clk

output wire afi_phy_clk, // .afi_phy_clk

output wire pll_avl_phy_clk // .pll_avl_phy_clk

);

其中的output wire [14:0] mem_a, // memory.mem_a

output wire [2:0] mem_ba, // .mem_ba

output wire [0:0] mem_ck, // .mem_ck

output wire [0:0] mem_ck_n, // .mem_ck_n

output wire [0:0] mem_cke, // .mem_cke

output wire [0:0] mem_cs_n, // .mem_cs_n

output wire [1:0] mem_dm, // .mem_dm

output wire [0:0] mem_ras_n, // .mem_ras_n

output wire [0:0] mem_cas_n, // .mem_cas_n

output wire [0:0] mem_we_n, // .mem_we_n

output wire mem_reset_n, // .mem_reset_n

inout wire [15:0] mem_dq, // .mem_dq

inout wire [1:0] mem_dqs, // .mem_dqs

inout wire [1:0] mem_dqs_n, // .mem_dqs_n

output wire [0:0] mem_odt, // .mem_odt

是DDR3的接口,请问您说的面向用户的接口产生读写时序,如实现向DDR3写数据操作,是我直接给DDR3的DQ赋给数据就可以么?哪些信号是用户接口用于实现写操作呢?

谢谢您啦,对DDR3这块儿真的是不太明白

你好,你的DDR3调试的怎么样了?最近我也在调,想咨询你几个问题

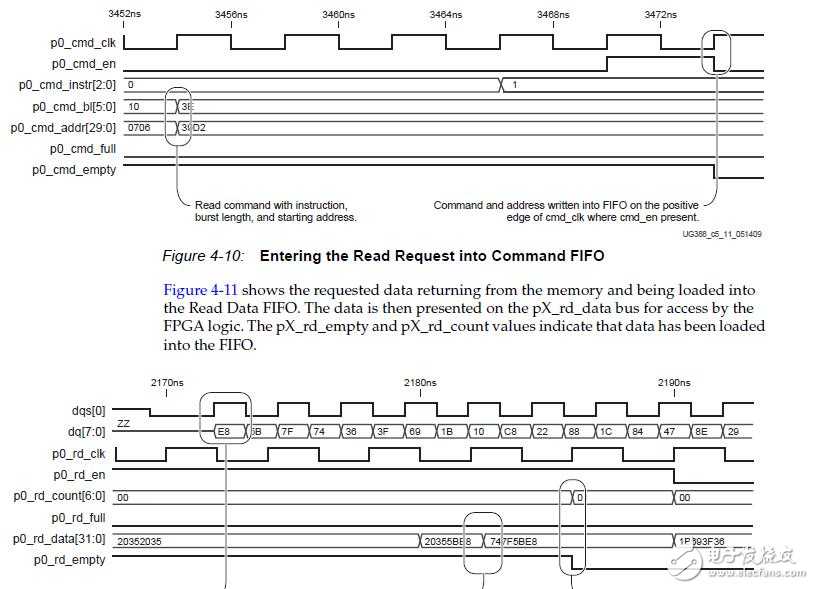

当然不能直接写,直接写还要MIG干啥,附图是你要配置的时序,MIG通过FIFO将用户数据和DDR相连,写数据时先将数据通过写入口或者双向口写入写FIFO,然后给写请求命令,MIG就会产生相应的时序将数据写入DDR,读的时候先给读请求命令,MIG会将数据读回来放在读FIFO里,然后再通过读出口读取数据

你好大神,最近在调试xilinx的ddr3,由于开发板的问题,我必须把生成的ddr差分时钟改为单端时钟然后在自己添加个pll的ip接到ddr上,我想知道怎么把ddr的差分时钟改为单端时钟,然后怎么和pll相连,敬请大神指点迷经。

大神们 小弟新人, 我最近在调试 ddr3,我这边用altera 生成ddr3的ip核 ,这边该怎么调试啊