FPGA之上升沿检测

`timescale 1ns / 1ps

module PD_up(

clk , //系统时钟 50MHz ;

rest_n , //系统复位信号 低电平有效 ;

signal_in , //待检测信号输入 ;

rising_flag //上升沿标 ;

);

input clk ;

input signal_in ;

input rest_n ;

output rising_flag ;

/****************************************************************

signal_in 0 0 0 1 1 0

~signal_in 1 1 1 0 0 1

signal_in_d 0 0 0 1 1 0

-----------------------------

rising_flag 0 0 0 0 1 signal_in_d & ~signal_in 下降沿检测

1 1 0 1 1

0 0 1 0 0 ~[signal_in_d | ~signal_in] 上升沿检测

***************************************************************/

reg signal ; //待检测信号输入寄存器;

reg rising_flag ; //上升沿标寄存器,值为 1 被检信号上升沿到来;

reg signal_in_d ; //signal_in_d 比 signal_in延迟一个时钟周期;

always@(posedge clk or negedge rest_n)begin

if(!rest_n)begin

signal <= 0;

end

else begin

signal <= signal_in;

end

end

always@(posedge clk or negedge rest_n)begin

if(!rest_n)begin

signal_in_d <= 0;

end

else begin

signal_in_d <= signal;

end

end

always@(*)begin //上升沿检测;

rising_flag = ~((~signal) | signal_in_d);

end

endmodule

测试代码:

module tb_PD_up;

// Inputs

reg clk;

reg rest_n;

reg signal_in;

// Outputs

wire rising_flag;

// Instantiate the Unit Under Test (UUT)

PD_up uut (

.clk(clk),

.rest_n(rest_n),

.signal_in(signal_in),

.rising_flag(rising_flag)

);

initial begin

// Initialize Inputs

clk = 0;

// Wait 100 ns for global reset to finish

#100;

forever #10 clk = ~clk;

// Add stimulus here

end

initial begin

rest_n = 0;

#100;

rest_n = 1;

end

initial begin

signal_in = 0;

#100;

#200 signal_in = 0;

#50 signal_in = 1;

#100 signal_in = 0;

#300 signal_in = 1;

#50 signal_in = 0;

end

endmodule

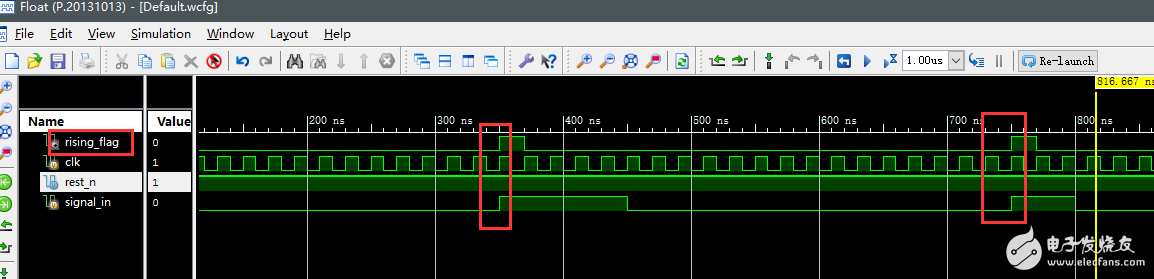

仿真波形。

仿真波形。

仿真波形。

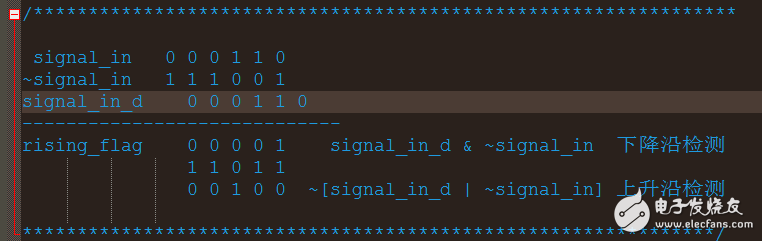

- /****************************************************************

- signal_in 0 0 0 1 1 0

- ~signal_in 1 1 1 0 0 1

- signal_in_d 0 0 0 1 1 0

- -----------------------------

- rising_flag 0 0 0 0 1 signal_in_d & ~signal_in 下降沿检测

- 1 1 0 1 1

- 0 0 1 0 0 ~[signal_in_d | ~signal_in] 上升沿检测

- ***************************************************************/

加载代码缩进怎么跟我写程序不一样啊。这里面~signal_in是signal的取反。signal_in_d比signal_in滞后一个时钟周期

这里是上升沿检测的原理说明:下降沿跟上升沿检测稍微有点区别。

待会儿写下降沿检测,如有错误还望,各位大神批评指正!

下降沿检测verilog代码

- `timescale 1ns / 1ps

- /************************************************

- 下降沿检测verilog代码

- 原理:signal = signal_in

- signal 0 0 0 1 1 0

- ~signal 1 1 1 0 0 1

- signal_d 0 0 0 1 1 0

- ----------------------------

- falling_flag 0 0 0 0 1

-

- falling_flag = (~signal) & signal_d

- ************************************************/

- module PD_dn(

- clk , //系统时钟 50MHz;

- rest_n , //系统复位信号,低电平有效;

- signal_in , //被检信号输入;

- falling_flag //下降沿检测输出标志;

- );

- input clk ;

- input rest_n ;

- input signal_in ;

- output falling_flag ;

- reg signal ;

- reg signal_d ;

- reg falling_flag ;

- always@(*)begin

- signal <= signal_in;

- end

- /********得到滞后signal一个时钟周期的signal_d********/

- always@(posedge clk or negedge rest_n)begin

- if(!rest_n)begin

- signal_d <= 0;

- end

- else begin

- signal_d <=signal;

- end

- end

- /*******************下降沿标志***********************/

- always@(*)begin

- if(!rest_n)begin

- falling_flag <= 0;

- end

- else begin

- falling_flag <= (~signal) & signal_d;

- end

- end

-

- endmodule

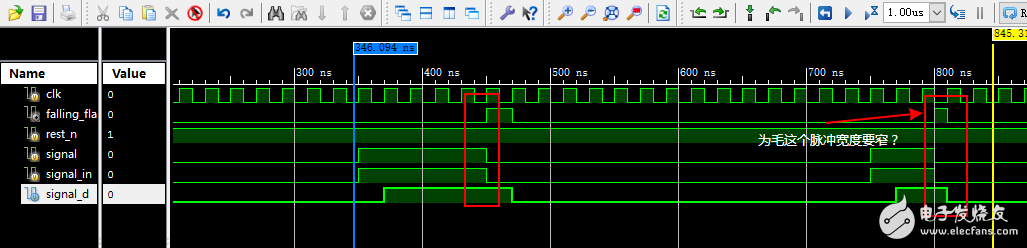

仿真波形

仿真波形

仿真波形

测试代码跟上面的一样