问一下关于pll的问题

时间:10-02

整理:3721RD

点击:

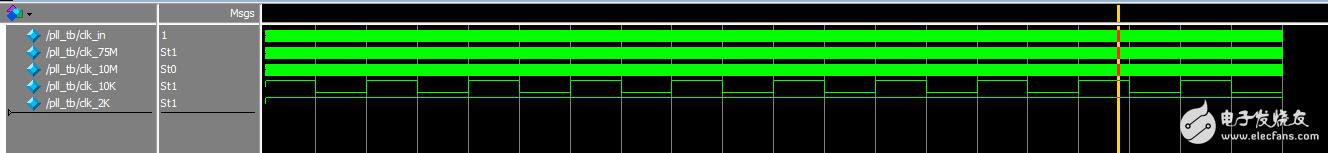

初学者,要用一个50MHz的时钟,生成75MHz、10MHz、10KHz、2KHz的时钟,用一个pll实现不了,就用了如下方式:

pll1 p1(.inclk0(clk_in),.c0(clk_75M),.c1(clk_10M));

pll2 p2(.inclk0(clk_10M),.c0(clk_2K),.c1(clk_10K));

波形是:

为什么clk_2K始终是1.

还有之前试过:

pll1 p1(.inclk0(clk_in),.c0(clk_75M),.c1(clk_10M));

pll2 p2(.inclk0(clk_in),.c0(clk_2K),.c1(clk_10K));

modelsim直接没有波形,是一个外部始终输入不能同时用作两个pll输入吗?

pll1 p1(.inclk0(clk_in),.c0(clk_75M),.c1(clk_10M));

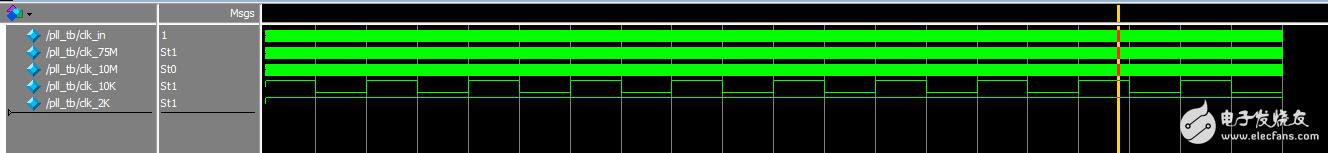

pll2 p2(.inclk0(clk_10M),.c0(clk_2K),.c1(clk_10K));

波形是:

为什么clk_2K始终是1.

还有之前试过:

pll1 p1(.inclk0(clk_in),.c0(clk_75M),.c1(clk_10M));

pll2 p2(.inclk0(clk_in),.c0(clk_2K),.c1(clk_10K));

modelsim直接没有波形,是一个外部始终输入不能同时用作两个pll输入吗?

支持一下,感谢分享~~~

我个人的观点哦:PLL内部应该有倍频和分频以及锁相环的模块;如其倍频最大的比例为M,分频最大为N,故PLL输出的最高时钟为M*fin,最低为fin/N;

所以我觉得会不会是你的PLL分频的倍数超出了你使用的IP核的限制了

其实你没必要使用两个PLL的,10K与2K时钟可以使用always语句来分频就好了