vivoda仿真时钟出现异常现象

时间:10-02

整理:3721RD

点击:

最近在仿真一个工程,出现一个奇怪的现象,先描述一下我的问题

//我的TB 中的时钟块 : 四个时钟,有两个有门控

assign iclk = (iclk_en) ? iclk_gen : `CLK_DISEN ;

assign oclk = (oclk_en) ? oclk_gen : `CLK_DISEN ;

always #(`I_PERIOD/2) iclk_gen = ~iclk_gen ;

always #(`O_PERIOD/2) oclk_gen = ~oclk_gen ;

always #(`DDR_CLK_PERIOD/2) ddr_clk = ~ddr_clk ;

always #(`DDR_REF_PERIOD/2) ddr_ref_clk = ~ddr_ref_clk ;

//下面我的initial 块

initial begin

task1;

task2 ;

task3 ;

.....

end

// task 区

//----------------------

task task1 ; begin

oclk_en = `DISABLE ;

dvalid_in = `DISABLE ;

.

//reset delay

......

oclk_en = `ENABLE ;

dvalid_in = `ENABLE ;

end

//----------------------

task task2 ; begin

oclk_en = `ENABLE ;

dvalid_in = `ENABLE ;

.

end

//----------------------

task task3 ; begin

oclk_en = `ENABLE ;

dvalid_in = `ENABLE ;

.

end

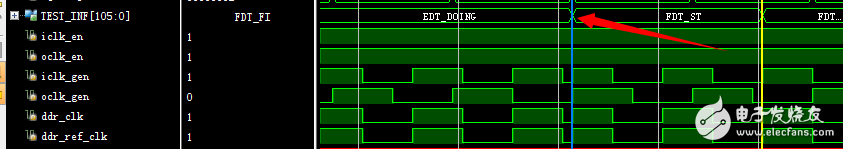

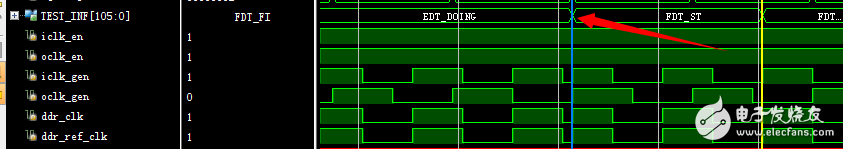

结果在执行到task3 的时候出现了波形“打盹”的现象。红色箭头就是task3的起始时间点

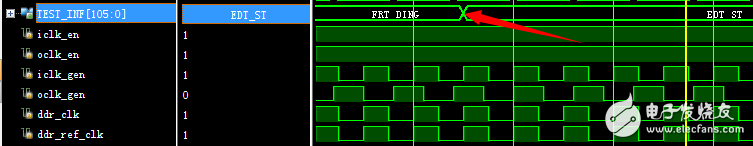

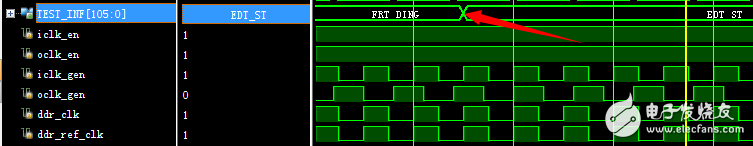

既然task3出现这种现象,我就去找task2.结果发现task2又是完好的。红色箭头就是task2的起始时间点

本来就应该是都不会出现这种“打盹”现象吧。

那是哪里出了问题导致这个奇怪的现象呢?

提示:是gen出现了问题,门控在gen发生器后面。再说了这是个TB门控也没有关系吧

//我的TB 中的时钟块 : 四个时钟,有两个有门控

assign iclk = (iclk_en) ? iclk_gen : `CLK_DISEN ;

assign oclk = (oclk_en) ? oclk_gen : `CLK_DISEN ;

always #(`I_PERIOD/2) iclk_gen = ~iclk_gen ;

always #(`O_PERIOD/2) oclk_gen = ~oclk_gen ;

always #(`DDR_CLK_PERIOD/2) ddr_clk = ~ddr_clk ;

always #(`DDR_REF_PERIOD/2) ddr_ref_clk = ~ddr_ref_clk ;

//下面我的initial 块

initial begin

task1;

task2 ;

task3 ;

.....

end

// task 区

//----------------------

task task1 ; begin

oclk_en = `DISABLE ;

dvalid_in = `DISABLE ;

.

//reset delay

......

oclk_en = `ENABLE ;

dvalid_in = `ENABLE ;

end

//----------------------

task task2 ; begin

oclk_en = `ENABLE ;

dvalid_in = `ENABLE ;

.

end

//----------------------

task task3 ; begin

oclk_en = `ENABLE ;

dvalid_in = `ENABLE ;

.

end

结果在执行到task3 的时候出现了波形“打盹”的现象。红色箭头就是task3的起始时间点

既然task3出现这种现象,我就去找task2.结果发现task2又是完好的。红色箭头就是task2的起始时间点

本来就应该是都不会出现这种“打盹”现象吧。

那是哪里出了问题导致这个奇怪的现象呢?

提示:是gen出现了问题,门控在gen发生器后面。再说了这是个TB门控也没有关系吧

忘记说明了, oclk_gen 时钟始终都没有问题。

问题已经解决。原来是后面又对gen进行了赋值。之前那个刚好在上升沿,所以没有影响