时序分析总结(以SDRAM时序约束为例)

时间:10-02

整理:3721RD

点击:

1。时序分析就是分析前级的数据是否在后一个时钟沿的数据有效窗口里面,就是说在整个窗口内部,数据都应该保持有效,如果不满足时间窗的前端,就是setup违例,如果不满足时间窗的后端,那么就是hold违例;

2.分析的基本情况是针对reg2reg这种情况,至于pin-2-reg,给出pin端的时间窗,来约束FPGA的su和hd时间,对于reg-2-pin,给出外部的时间窗,来约束FPGA内部的tco等参数,要约束的始终是FPGA内部,要假定外部提要求,FPGA内部通过一定的布局来满足;

3.关于inputmin/max,outputmin/max这些参数都是为了给出有效时间窗口的范围,所以切记,这些值都是以clock为基准的,记住这个,算的时候就很容易了;

4.基本的时序约束有:时钟约束,IO约束,例外说明,这些都是可以通过timequest来设置的。所谓同步时序,寄存器在同一个时钟沿动作,所谓异步时序,寄存器不是一个时钟沿动作,还有源同步时序,就是原始clk是一致的,但是使用的时候可能同频不同相。可以看到,这是设计电路的固有属性,跟约束无关,现在我们要通过上面的3中约束来正确的分析这3中电路结构。

5.明确一下,基本的分析模型,对于reg2reg,对于setup的分析是,sourceclk和destinationclk中寻找有效沿靠得最近的两个来分析,同时满足:sourceclk在前destination在后,这样,前面的为lauchedge,后面的是latchedge,这就是setuprelations分析,注意,找这两个有效沿的时候,时钟走线延迟是不计算在内的(不然,各个寄存器离clk有远有近,这个延时都不相同,就不好找了)。同时,如果两个沿的时间差为0,也是忽略的。

6.平时,都是按照默认的模型来分析的,即,对于同步时序,前一个clocklauch,后一个clocklatch,这是绝大多数情况。对于其他不同频同相得时钟,都要找2个相近的沿来分析。有时候,找到的2个沿就不是我们实际使用的latch~lauch沿,这个时候就需要例外设置了。

7.一旦setuprelation的2个沿确定了,hold的2个沿也就确定了,对于同频的时钟来讲,如果不同频,还需要找holdrelation的2个沿,在handbook上有讲怎么找。

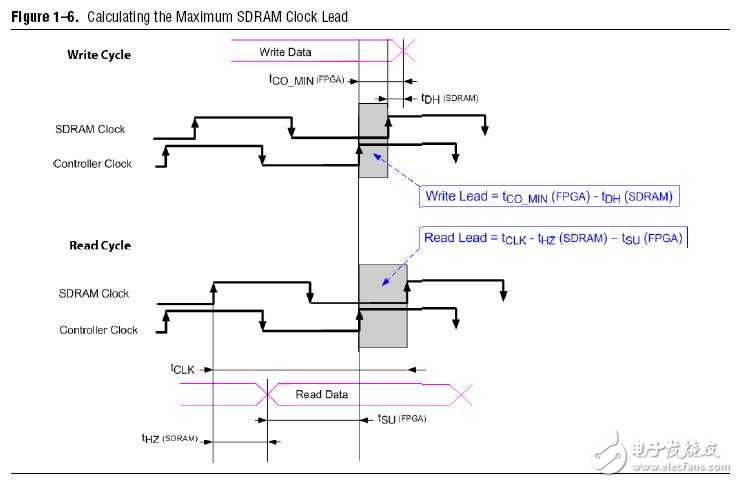

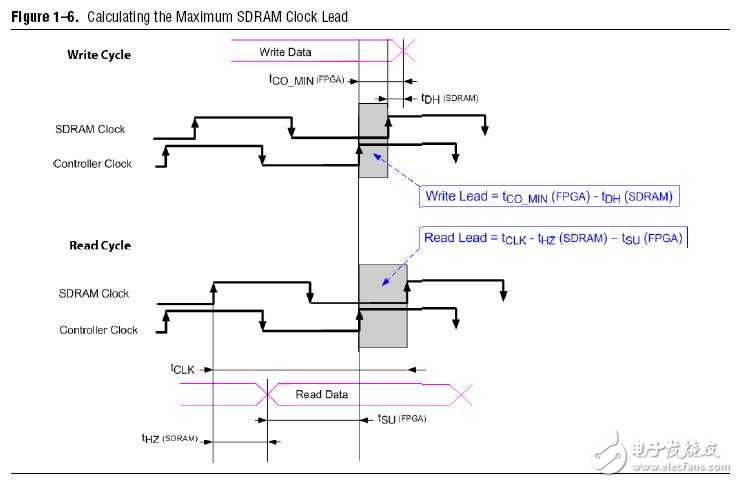

8..对于SDRAM时序的来讲,分析好相移,最后确定了我们实际用的setuprelation和holdrelation关系如下:

也就是SDRAMclk需要phaseshift2ns左右,以从左到右记这四个risingedge,1,2,3,4;

对于读:SDRAMclock2launch-->Controllerclock3latch,按照默认模型分析,setuprelation就是对的;

对于写:Controllerclock1launch->SDRAMclock4latch,这时,默认的setuprelation关系是:Controllerclock1launch->SDRAMclock2latch,这个显然是不满足的,通过多周期的例外设置来调整setuprelation如我们想要的来分析;

上面分析的是setuprelation,对于同频的clk来讲,setup的关系对了,hold的关系自然也对了。

9。上例中,sdram的data是根据sdramclk来确定outputmax/min的,因为在write的时候,我们要给出的外部sdram中reg的timewindow。

2.分析的基本情况是针对reg2reg这种情况,至于pin-2-reg,给出pin端的时间窗,来约束FPGA的su和hd时间,对于reg-2-pin,给出外部的时间窗,来约束FPGA内部的tco等参数,要约束的始终是FPGA内部,要假定外部提要求,FPGA内部通过一定的布局来满足;

3.关于inputmin/max,outputmin/max这些参数都是为了给出有效时间窗口的范围,所以切记,这些值都是以clock为基准的,记住这个,算的时候就很容易了;

4.基本的时序约束有:时钟约束,IO约束,例外说明,这些都是可以通过timequest来设置的。所谓同步时序,寄存器在同一个时钟沿动作,所谓异步时序,寄存器不是一个时钟沿动作,还有源同步时序,就是原始clk是一致的,但是使用的时候可能同频不同相。可以看到,这是设计电路的固有属性,跟约束无关,现在我们要通过上面的3中约束来正确的分析这3中电路结构。

5.明确一下,基本的分析模型,对于reg2reg,对于setup的分析是,sourceclk和destinationclk中寻找有效沿靠得最近的两个来分析,同时满足:sourceclk在前destination在后,这样,前面的为lauchedge,后面的是latchedge,这就是setuprelations分析,注意,找这两个有效沿的时候,时钟走线延迟是不计算在内的(不然,各个寄存器离clk有远有近,这个延时都不相同,就不好找了)。同时,如果两个沿的时间差为0,也是忽略的。

6.平时,都是按照默认的模型来分析的,即,对于同步时序,前一个clocklauch,后一个clocklatch,这是绝大多数情况。对于其他不同频同相得时钟,都要找2个相近的沿来分析。有时候,找到的2个沿就不是我们实际使用的latch~lauch沿,这个时候就需要例外设置了。

7.一旦setuprelation的2个沿确定了,hold的2个沿也就确定了,对于同频的时钟来讲,如果不同频,还需要找holdrelation的2个沿,在handbook上有讲怎么找。

8..对于SDRAM时序的来讲,分析好相移,最后确定了我们实际用的setuprelation和holdrelation关系如下:

也就是SDRAMclk需要phaseshift2ns左右,以从左到右记这四个risingedge,1,2,3,4;

对于读:SDRAMclock2launch-->Controllerclock3latch,按照默认模型分析,setuprelation就是对的;

对于写:Controllerclock1launch->SDRAMclock4latch,这时,默认的setuprelation关系是:Controllerclock1launch->SDRAMclock2latch,这个显然是不满足的,通过多周期的例外设置来调整setuprelation如我们想要的来分析;

上面分析的是setuprelation,对于同频的clk来讲,setup的关系对了,hold的关系自然也对了。

9。上例中,sdram的data是根据sdramclk来确定outputmax/min的,因为在write的时候,我们要给出的外部sdram中reg的timewindow。

好资料 感谢小编分享!

多谢小编分享,收藏啦

学习学习,谢谢分享!

好资料感谢小编分享!

学习了。

学习一下,谢谢!