有做过RS编码的吗?有个问题请教

时间:10-02

整理:3721RD

点击:

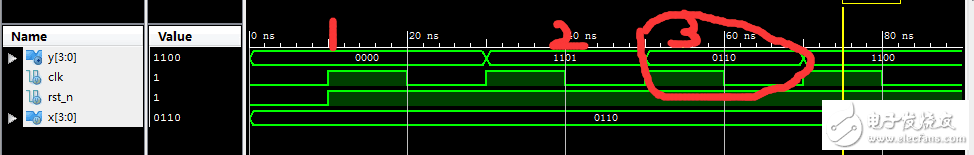

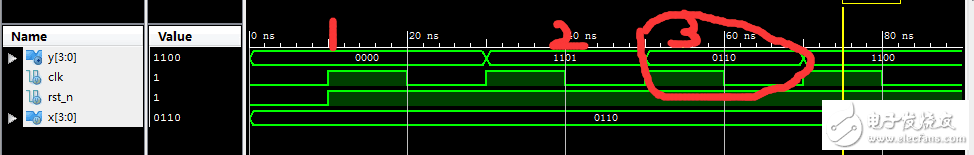

最近我在弄一个RS编码 然后根据线性移位反馈寄存器的推导写了代码 ,但在第三次移位的时候,与计算出来的值对不上,计算出来的值应该是1010,而我仿真出来是0110,

file:///D:\Documents\Tencent Files\1210438173\Image\C2C\FT6BT_F1]41T2V5SJ9RGS~F.png这是仿真图

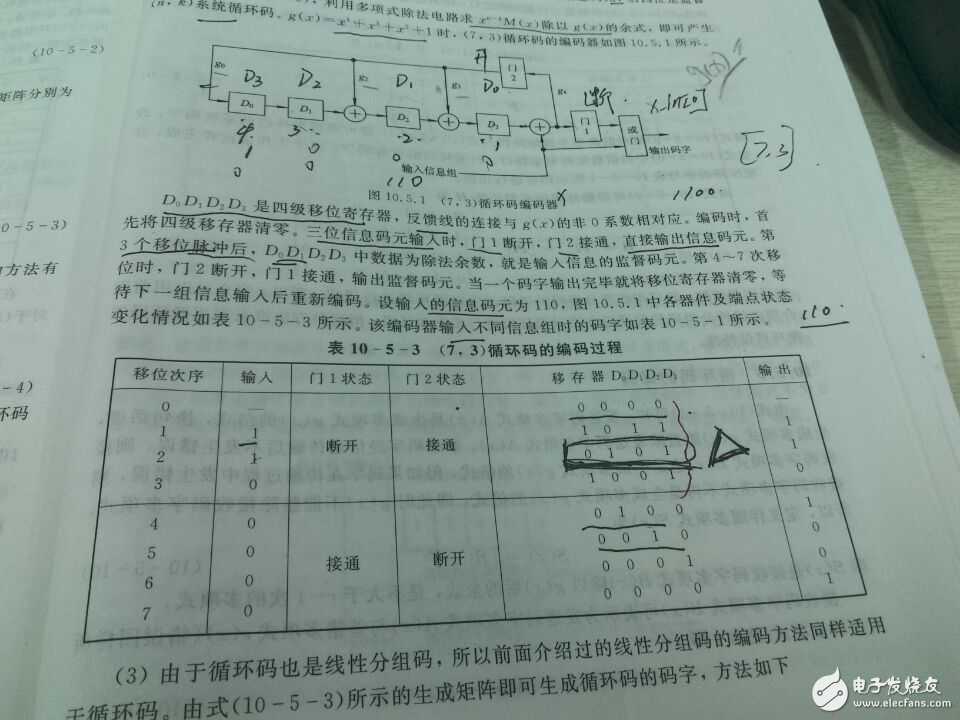

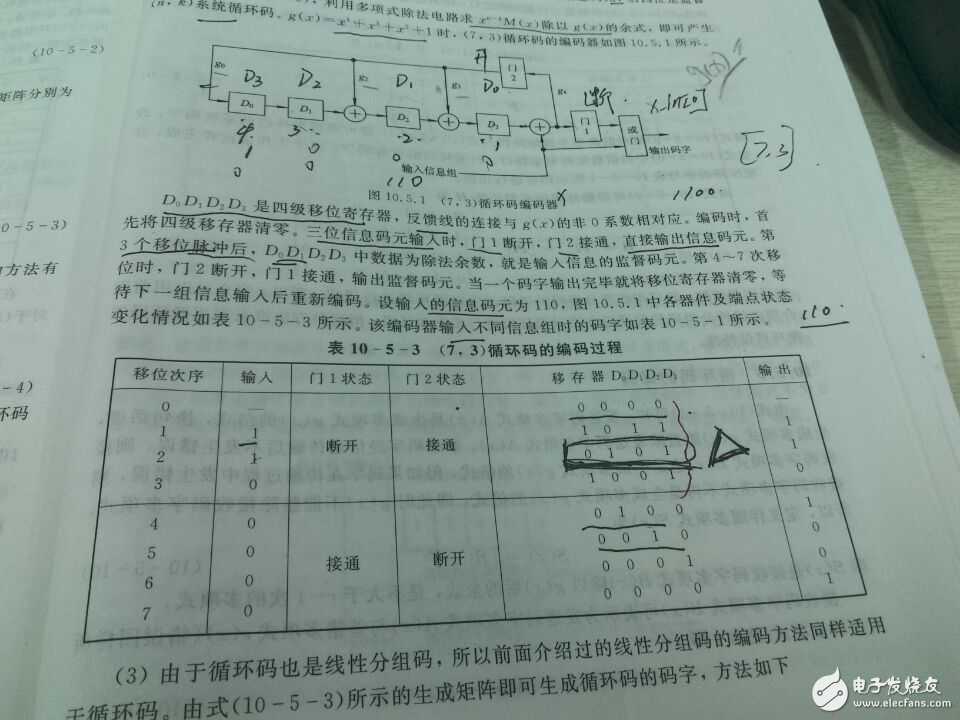

,这是书上的计算值,

,这是书上的计算值,

,他们对不上。

,他们对不上。

代码如下:

module frs(clk,rst_n,x,y

);

input clk;

input rst_n;

input [3:0] x;

output [3:0] y;

parameter idle=2'b00;

parameter second=2'b01;

parameter third=2'b10;

parameter forth=2'b11;

reg [1:0] state;

reg [3:0] D1;

// reg [3:0] x_in;

//reg [3:0] cnt;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

cnt<=4'b0000;

D1<=4'b1101;

state<=idle;

end

else

case(state)

idle:

begin

D1[0]<=x[3]^D1[3];

D1[1]<=D1[0];

D1[2]<=D1[1]^x[3];

D1[3]<=D1[2]^x[3];

state<=second;

end

second:

begin

D1[0]<=x[2]^D1[3];

D1[1]<=D1[0];

D1[2]<=D1[1]^x[2];

D1[3]<=D1[2]^x[2];

state<=third;

end

third:

begin

D1[0]<=x[1]^D1[3];

D1[1]<=D1[0];

D1[2]<=D1[1]^x[1];

D1[3]<=D1[2]^x[1];

state<=forth;

end

forth:

begin

D1[0]<=x[0]^D1[3];

D1[1]<=D1[0];

D1[2]<=D1[1]^x[0];

D1[3]<=D1[2]^x[0];

end

default:state<=idle;

endcase

end

assign y=D1;

endmodule

file:///D:\Documents\Tencent Files\1210438173\Image\C2C\FT6BT_F1]41T2V5SJ9RGS~F.png这是仿真图

,这是书上的计算值,

,这是书上的计算值, ,他们对不上。

,他们对不上。代码如下:

module frs(clk,rst_n,x,y

);

input clk;

input rst_n;

input [3:0] x;

output [3:0] y;

parameter idle=2'b00;

parameter second=2'b01;

parameter third=2'b10;

parameter forth=2'b11;

reg [1:0] state;

reg [3:0] D1;

// reg [3:0] x_in;

//reg [3:0] cnt;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

cnt<=4'b0000;

D1<=4'b1101;

state<=idle;

end

else

case(state)

idle:

begin

D1[0]<=x[3]^D1[3];

D1[1]<=D1[0];

D1[2]<=D1[1]^x[3];

D1[3]<=D1[2]^x[3];

state<=second;

end

second:

begin

D1[0]<=x[2]^D1[3];

D1[1]<=D1[0];

D1[2]<=D1[1]^x[2];

D1[3]<=D1[2]^x[2];

state<=third;

end

third:

begin

D1[0]<=x[1]^D1[3];

D1[1]<=D1[0];

D1[2]<=D1[1]^x[1];

D1[3]<=D1[2]^x[1];

state<=forth;

end

forth:

begin

D1[0]<=x[0]^D1[3];

D1[1]<=D1[0];

D1[2]<=D1[1]^x[0];

D1[3]<=D1[2]^x[0];

end

default:state<=idle;

endcase

end

assign y=D1;

endmodule

有人吗?柑橘还是不知道买哪里错了