TOSHIBA TCD2901D CCD驱动代码

时间:10-02

整理:3721RD

点击:

TOSHIBA TCD2901D CCD驱动代码

module DriveCCD(

clk_sys,

rst_n,

clk_1M,

clk_sh,

clk_500k_1A,

clk_500k_2A,

clk_1M_rs,

clk_1M_cp

);

input clk_sys;

input rst_n;

output clk_1M;

output clk_sh;

output clk_500k_1A;

output clk_500k_2A;

output clk_1M_rs;

output clk_1M_cp;

reg [7:0] Cnt8;

reg [7:0] Cnt_A8;

reg [7:0] Cnt_B8;

reg [7:0] Cnt_C8;

reg [7:0] Cnt_delay1;

reg [7:0] Cnt_delay2;

reg [15:0] Cntsh;

reg clk_1M;

reg clk_sh;

reg clk_500k_1A;

reg clk_500k_2A;

reg clk_1M_rs;

reg clk_1M_cp;

always @(posedge clk_sys or negedge rst_n)

begin

if (!rst_n)

begin

clk_1M <= 0;

Cnt8 <= 8'b0;

end

else if(Cnt8 == 8'd24)

begin

clk_1M <= ~clk_1M;

Cnt8 <= 8'b0;

end

else

Cnt8 <= Cnt8 + 8'b1;

end

always @(posedge clk_1M or negedge rst_n)

begin

if (rst_n ==1'b0)

begin

Cntsh <= 16'b0;

clk_sh <= 1;

end

else if(Cntsh == 16'd20)

begin

clk_sh <= ~clk_sh;

Cntsh <= Cntsh + 16'b1;

end

else if(Cntsh == 16'd10655)

begin

clk_sh <= ~clk_sh;

Cntsh <= 16'b0;

end

else

Cntsh <= Cntsh + 16'b1;

end

always @(posedge clk_sys or negedge rst_n)

begin

if (rst_n ==1'b0)

begin

clk_500k_1A <= 'b1;

clk_500k_2A <= 'b0;

Cnt_A8 <= 8'b0;

end

else if(clk_sh == 0)

begin

if(Cnt_A8 == 8'd49)

begin

clk_500k_1A <= ~clk_500k_1A;

clk_500k_2A <= ~clk_500k_2A;

Cnt_A8 <= 8'b0;

end

else

Cnt_A8 <= Cnt_A8 + 8'b1;

end

else

begin

clk_500k_1A <= 'b1;

clk_500k_2A <= 'b0;

end

end

always @(posedge clk_sys or negedge rst_n)

begin

if(rst_n ==1'b0)

Cnt_delay1 <= 8'b0;

else if(clk_sh==0)

begin

if(Cnt_delay1 == 8'd40)

Cnt_delay1 <= Cnt_delay1;

else

Cnt_delay1 <= Cnt_delay1 + 8'b1;

end

else

Cnt_delay1 <= 8'b0;

end

always @(posedge clk_sys or negedge rst_n)

begin

if(rst_n ==1'b0)

Cnt_delay2 <= 8'b0;

else if(clk_sh==0)

begin

if(Cnt_delay2 == 8'd45)

Cnt_delay2 <= Cnt_delay2;

else

Cnt_delay2 <= Cnt_delay2 + 8'b1;

end

else

Cnt_delay2 <= 8'b0;

end

always @(posedge clk_sys or negedge rst_n)

begin

if (rst_n ==1'b0)

begin

clk_1M_rs <= 1;

Cnt_B8 <= 8'b0;

end

else if(clk_sh == 0 && Cnt_delay1 == 8'd40)

begin

if(Cnt_B8 == 8'd27)

begin

clk_1M_rs <= ~clk_1M_rs;

Cnt_B8 <= Cnt_B8 + 8'b1;

end

else if(Cnt_B8 == 8'd40)

begin

clk_1M_rs <= ~clk_1M_rs;

Cnt_B8 <= Cnt_B8 + 8'b1;

end

else if(Cnt_B8 == 8'd49)

Cnt_B8 <= 8'b0;

else

Cnt_B8 <= Cnt_B8 + 8'b1;

end

else begin

clk_1M_rs <= 1;Cnt_B8 <= 8'b0;end

end

always @(posedge clk_sys or negedge rst_n)

begin

if (rst_n ==1'b0)

begin

clk_1M_cp <= 1;

Cnt_C8 <= 8'b0;

end

else if(clk_sh == 0 && Cnt_delay2 == 8'd45)

begin

if(Cnt_C8 == 8'd36)

begin

clk_1M_cp <= ~clk_1M_cp;

Cnt_C8 <= Cnt_C8 + 8'b1;

end

else if(Cnt_C8 == 8'd48)

begin

clk_1M_cp <= ~clk_1M_cp;

Cnt_C8 <= Cnt_C8 + 8'b1;

end

else if(Cnt_C8 == 8'd49)

Cnt_C8 <= 8'b0;

else

Cnt_C8 <= Cnt_C8 + 8'b1;

end

else begin

clk_1M_cp <= 1;Cnt_C8 <= 8'b0;end

end

endmodule

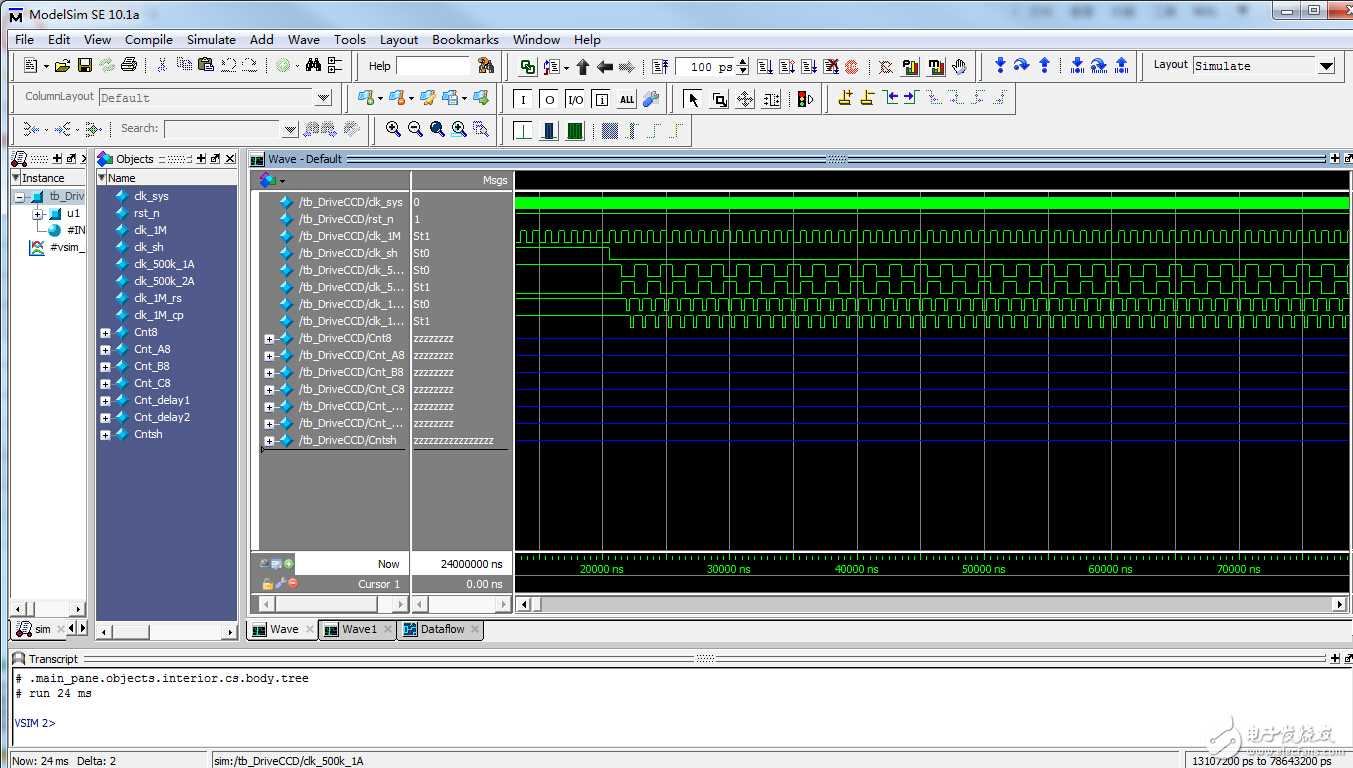

测试程序

`timescale 1ns/1ps

module tb_DriveCCD;

reg clk_sys;

reg rst_n;

wire clk_1M;

wire clk_sh;

wire clk_500k_1A;

wire clk_500k_2A;

wire clk_1M_rs;

wire clk_1M_cp;

DriveCCD u1(

.clk_sys(clk_sys),

.rst_n(rst_n),

.clk_1M(clk_1M),

.clk_sh(clk_sh),

.clk_500k_1A(clk_500k_1A),

.clk_500k_2A(clk_500k_2A),

.clk_1M_rs(clk_1M_rs),

.clk_1M_cp(clk_1M_cp)

);

initial

begin

rst_n=0;

#20

rst_n=1;

forever

begin

#10 clk_sys = 1;

#10 clk_sys = 0;

end

end

endmodule