关于CYCLOINE IV功耗和下载的问题

时间:10-02

整理:3721RD

点击:

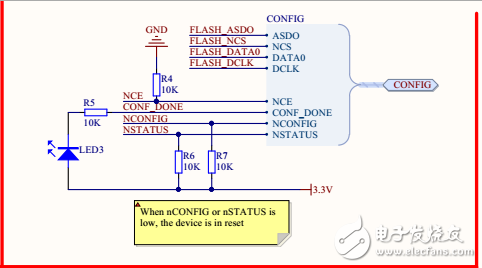

RT,我想问问CYCLONE IV系列115F484的一般最低功耗是多少,现在对该芯片四个2.5V的模拟PLL电源引脚选型独立的电源芯片。我想问下这四个管脚输入对于电流最大的需求是多少,如果我选择3.3V转2.5的电源的一款芯片最大输出电流是150mA是否够用,之前设计 的是5V转3.3V 的芯片提供的是最大1A 的电流这个肯定够用,但是这样的话就存在这样一个问题,下载的时候仿真器提供的3.3V电源转不了2.5V,这样的话就不能直接通过仿真器下载。

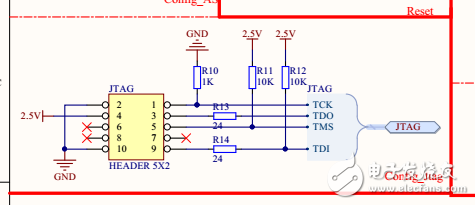

特别想问下大家,对于该系列芯片你们下载的时候是怎么设计的,是直接通过仿真器就下载了,还是通过外部供电再通过仿真器下载。

特别想问下大家,对于该系列芯片你们下载的时候是怎么设计的,是直接通过仿真器就下载了,还是通过外部供电再通过仿真器下载。

参考微雪电子的做法就可以了。建议5转2.5,说是低压差,但在这样的压差下性能好点,可以最小电流大点考虑500毫安的,有很多,对于1.2的建议1.5安的

现在的电路就是5V转2.5V 的设计。这样的设计插上3.3V的仿真下载口就不能直接下载

Jtag是2。5V的AS是3.3V的,除了这个原因 可能是布线的关系。

就不能直接下载 是什么意思