麻烦各位帮我看一下,出现下面的代码出现什么问题?怎么解决?

input clk,

input rst_n,

output [1:0] Column_scan

);

reg [18:0] counter1;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

counter1<=19'd0;

else if(counter1==499_999)

counter1<=19'd0;

else

counter1<=counter1+1'b1;

end

reg[1:0] t;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

t<=2'd0;

else if(t==2'd2)

t<=2'd0;

else

t<=t+1'b1;

end

reg [1:0] Column_scan_0;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

Column_scan_0<=2'b10;

else if(counter1==4999_999)

case(t)

2 'd0: Column_scan_0<=2'b10;

2 'd1: Column_scan_0<=2'b01;

endcase

end

assign Column_scan=Column_scan_0;

endmodule

1

module Column_scan_seg(

clk ,

rst_n ,

Column_scan

);

input clk ;

input rst_n ;

output [1:0] Column_scan ;

wire [1:0] Column_scan ;

reg [18:0] counter1 ;

reg [1:0] t ;

reg [1:0] Column_scan_0 ;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

counter1<=0;

end

else if(counter1==4_999_999) begin

counter1<=0;

end

else

counter1<=counter1+1;

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

t<=0;

end

else if(counter1==4_999_999) begin

if(t==2)

t<=0;

else

t<=t+1;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

Column_scan_0<=2'b10;

end

else begin

case(t)

0: Column_scan_0<=2'b10;

1: Column_scan_0<=2'b01;

endcase

end

end

assign Column_scan = Column_scan_0 ;

endmodule

不太好弄?

怎么讲?

t 是能取到2的,你case语句并没有对此情况进行考虑,第二个10ms Column_scan_0就会等于不定值

当然,我指的是你使用的时钟是50M才是对应的10ms~

这个代码真的还挺乱的

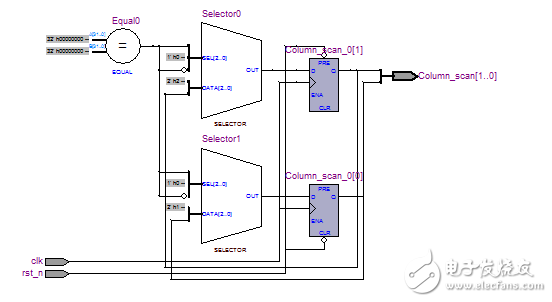

帮你修改了一下代码

谢谢各位的帮助!