XILINX ISE 13.4 时序仿真问题

时间:10-02

整理:3721RD

点击:

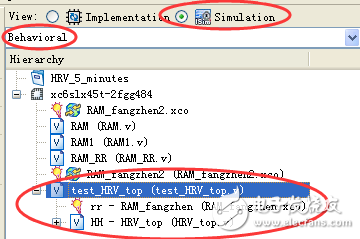

我使用ISE 13.4对设计的代码进行逻辑综合和布局布线等。写的测试文件调用了一个RAM IP核,见图1。

其中test_HRV_top为测试文件,调用了RAM_fangzhen这个IP核和设计顶层文件HRV_top。通过测试文件

对设计文件进行功能仿真,仿真结果正确。

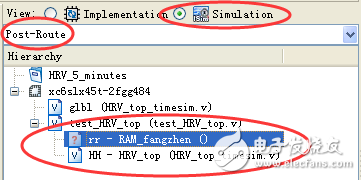

但是当我对设计完成布局布线之后,没有其它错误,接着进行时序仿真,见图2. 在图2中,测试文件调用的

RAM IP核(也就是RAM_fangzhen)怎么找不到啊?求高手解答。

其中test_HRV_top为测试文件,调用了RAM_fangzhen这个IP核和设计顶层文件HRV_top。通过测试文件

对设计文件进行功能仿真,仿真结果正确。

但是当我对设计完成布局布线之后,没有其它错误,接着进行时序仿真,见图2. 在图2中,测试文件调用的

RAM IP核(也就是RAM_fangzhen)怎么找不到啊?求高手解答。

图1

图2