ISE14.7与MODELSIM-SE10.1a联合仿真出现无法解决的问题

时间:10-02

整理:3721RD

点击:

电脑操作系统xp

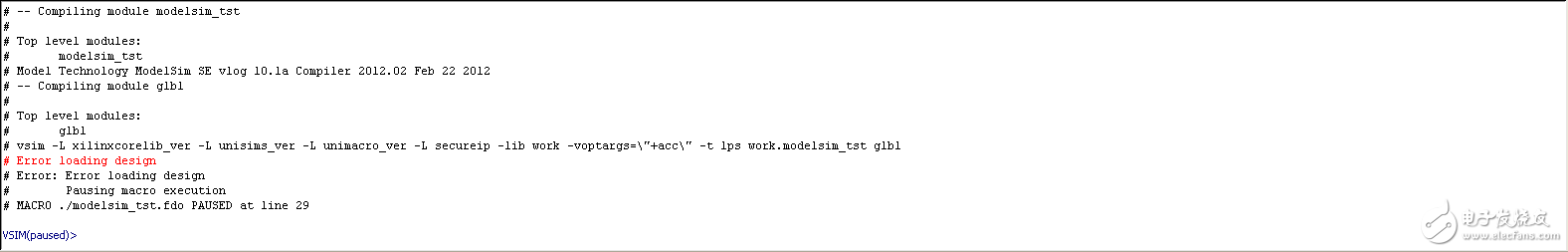

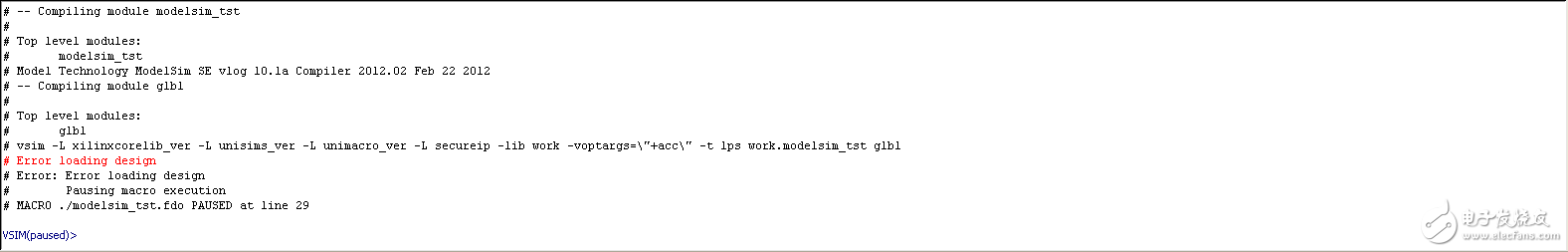

按照网上的教程,对ISE的库进行了编译,仿真软件路径设置也都设置好了,tb编写也没有语法问题,前一段时间好使,不知道什么时候,开始出现如下问题,怎么仿真都是下面的报错。求大神指点迷津。

按照网上的教程,对ISE的库进行了编译,仿真软件路径设置也都设置好了,tb编写也没有语法问题,前一段时间好使,不知道什么时候,开始出现如下问题,怎么仿真都是下面的报错。求大神指点迷津。

你建立的模块和实例化的模块在端口上不一致,有个检测哪个端口不一致的方法是:首先如果有多个实例化,把其他实例化全注释掉,只留一个实例化,看还有没有这个问题,找出是哪个实例化出现了问题;然后把实例化端口只保留一个、两个、···,判断是哪个端口出现了问题;最后就是看为什么这个端口有问题了:可能是实例规则写错了,比如.en(en_t),en是你实例化模块的端口,en_t是你顶层模块端口;也有可能实例化模块端口和顶层模块端口的数据类型定义错了

我的测试代码是这样编的,很简单,不会有错,我觉得是软件上连接上的错误。因为以前一直好使,现在不管什么仿真代码,都是报同一个错误。

- module modelsim(

- input clk,

- input rstn,

- input [7:0] a,

- output reg [7:0] b

- );

- always@(posedge clk or negedge rstn)

- if(!rstn) begin

- b<=8'h00;

- end

- else begin

- b<=a;

- end

- endmodule

- module modelsim_tst;

- // Inputs

- reg clk;

- reg rstn;

- reg [7:0] a;

- // Outputs

- wire [7:0] b;

- // Instantiate the Unit Under Test (UUT)

- modelsim uut (

- .clk(clk),

- .rstn(rstn),

- .a(a),

- .b(b)

- );

- initial begin

- clk=0;

- forever #5 clk=~clk;

- end

-

- initial begin

- rstn=0;

- #100 rstn=1;

- end

-

- initial begin

- a=8'h01;

- #25 a=8'h02;

- #25 a=8'h03;

- #25 a=8'h04;

- #25 a=8'h05;

- #25 a=8'h06;

- #25 a=8'h07;

- #25 a=8'h08;

-

- end

- endmodule