zynq零基础的进击之应用初体验20150525

第一次用SOC系统搭建,开机实验(上篇)给了我很大的鼓舞和信心,毕竟几乎没有摸过Zynq系列的片子。今天问题就出现了,下面是过程。

看着移植好的ubuntu,我感觉我只需要缝缝补补就能完成我的设计《基于Zynq 7系列Z-turn开发板的家庭影音及安全健康监控系统》。把光盘考下来,首先就发现了PL源工程,比较开心。

看了readme,一行字让我有点隐隐不安“vivado project withxylon display controller IP(logiCLK and logiCVC), required xylon licenses.”。logiCLK不像xilinx ipcore的命名风格啊,不管了,有工程入手毕竟可以快速理解带HDMI的设计是什么样子的。

首先从原理图看起(代码端口命令人各有意,不熟悉的设计不建议入手),F4~F4~,没反应,即使out of data也应该可以看啊,不行重编一下,这下麻烦了,不能编;

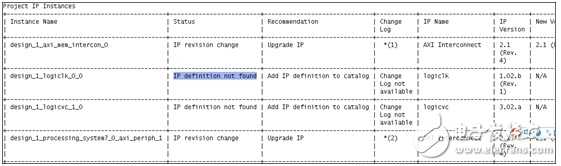

WARNING: [BD 41-1303] One or more IPs have been locked in the design'design_1.bd'. Please run report_ip_status for more details and recommendationson how to fix this issue.

输入“report_ip_status”;

果然就是这两个IP,我还是太年轻啊,其实人家都告诉我了的,网上搜了下,是xylon公司封装的ipcore,一年授权600,话说米尔能不能私下给我个试用的使一下?这个可能的话私下聊。我估计不行,只能自己解决。

Ps:这个工程现在看来太鸡肋了,不能编,不能看,也无法借鉴,PS的外围基本上用不了,建议不要放在盘里了。

现在梳理下解决方案:

目标:要能控制HDMI送显。

需要解决的问题:

hdmi_A、开发板外围连接是什么情况;

hdmi_B、PS-PL外设端口PL侧应该是什么样子,PS侧AXI互联怎么设计;

hdmi_C、PS侧数据如何搬移,包括外部存储(没用过ARM);

解决hdmi_A

当然是看原理图了,看原理图之前,我好奇的打开了_trd工程,期望能获取些心理,然而打开后,我感觉到了它对我满满的敌意。

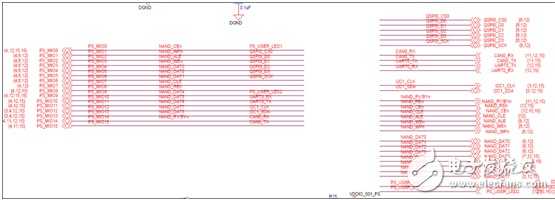

原来主逻辑只有一个PS,PL这边就是简单的管教驱动和LED送显之类的,我突然明白了,原来,这个开发板的目标是玩ARM啊,不然为啥是个Z7010撒,我感觉离目标又远了一步,不管怎么样,问题是要解决的。

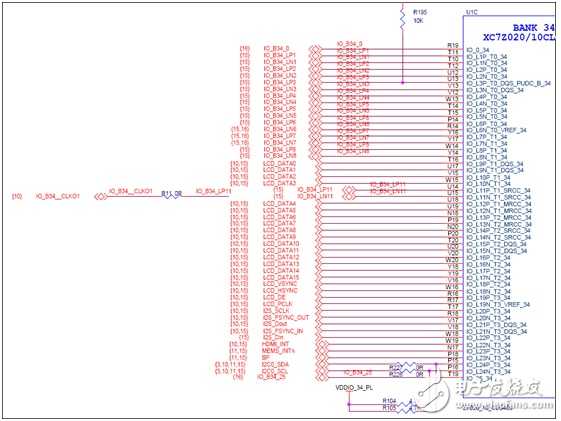

原理图打开,基本没啥可表的,就是对于管脚来说这个打印成pdf的还真不如给个excel表格,有些看不了,对设计可能带来问题,比如:

这个CLK01的目的是做冗余设计么?ture掉R11?

这块我有点看晕了,不管了,细节在设计的时候会解决的。

先从布局上看

U40、U43比较靠近HDMI接口,这个应该和送显有关,返回原理图看,为TDP12S016和SIL9022A.找手册

开发套件很贴心的给了一个,把手册大概读一遍,其中TDP12S016是一个HDMI的配套芯片,实际就是隔断单板数字并提供HDMI线驱动能力,以及连接保护、控制转换的一个A到B的端口,这也就不奇怪,其数据线为什么是U40、U43、J4的HDMI_txn是三端连接的了,这个是手册的推荐设计拉;

SIL9022A手册自己在网上下的,是HDMI的传输芯片,从管脚上很容易理解,RGB转HDMI_txn的,详细看手册,至此,外围接口基本明晰,需要把送显数据转换成RGB格式,HDMI_B也初现端倪。