关于modelsim仿真波形时序问题

时间:10-02

整理:3721RD

点击:

reg [7:0] temp;

reg [7:0] temp1;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

temp1 124)

temp <= 255;

else

temp <= 0;

end

assign Bina_img_out = temp;

endmodule

[img]file:///C:\Users\sola\AppData\Roaming\Tencent\Users\380514580\QQ\WinTemp\RichOle\QA2ZO[)GPB_QFC4[K3D4SIR.png[/img]

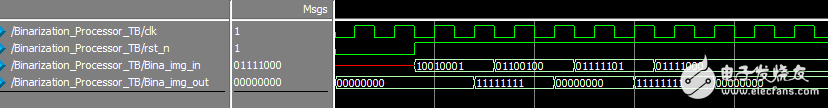

请问一 上面这段代码仿真出来的波形图怎么是这样的 不是时钟上升沿才处理吗? Bina_img_in应该往后推半个周期才对啊? 而且Bina_img_out应该是同步输出才是 怎么延后了一个半周期呢?求高手告知!

reg [7:0] temp1;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

temp1 124)

temp <= 255;

else

temp <= 0;

end

assign Bina_img_out = temp;

endmodule

[img]file:///C:\Users\sola\AppData\Roaming\Tencent\Users\380514580\QQ\WinTemp\RichOle\QA2ZO[)GPB_QFC4[K3D4SIR.png[/img]

请问一 上面这段代码仿真出来的波形图怎么是这样的 不是时钟上升沿才处理吗? Bina_img_in应该往后推半个周期才对啊? 而且Bina_img_out应该是同步输出才是 怎么延后了一个半周期呢?求高手告知!

我感觉会不会是引入两个temp变量后 引起的?