quartus 功能仿真没问题 可是时序仿真全乱了 怎么办啊大神们

时间:10-02

整理:3721RD

点击:

`timescale 1ns/100ps //测试文件

module Data_SCRAM_tb;

wire [7:0] Data_out;

wire k_flag;

reg[7:0] Data_in;

reg clk,rst;

initial

begin

clk=0;

rst=0;

#2 rst=1;

#1000

$stop();

end

always #10 clk=~clk;

always @(posedge clk or negedge rst)

begin

if(!rst)

Data_in<=8'b00000000;

else

Data_in<=Data_in+8'b00000001;

end

Data_SCRAM Dtest(.Data_in(Data_in),.Data_out(Data_out),.clk(clk),.rst(rst),.k_flag(k_flag));

endmodule

module Data_SCRAM(Data_in,Data_out,clk,rst,k_flag); //程序源码

input clk,rst;

input [7:0] Data_in;

output k_flag;

output [7:0] Data_out;

reg k_flag;

reg [7:0]Data_out;

reg [7:0] shift_reg;

reg [15:0] lfsr;

reg[7:0] scrambit;

reg[15:0] bit_out;

reg[15:0] lfsr_reg;

integer i;

task raoma;

begin

for(i=0;i<8;i=i+1) begin

scrambit[i]=Data_in[i]^lfsr[15-i];end

shift_reg[7:0]=scrambit[7:0];

end

endtask

task lfsr_shift;

begin

bit_out[0]=lfsr[8];

bit_out[1]=lfsr[9];

bit_out[2]=lfsr[10];

bit_out[3]=lfsr[11]^lfsr[8];

bit_out[4]=lfsr[12]^lfsr[9]^lfsr[8];

bit_out[5]=lfsr[13]^lfsr[10]^lfsr[9]^lfsr[8];

bit_out[6]=lfsr[14]^lfsr[11]^lfsr[10]^lfsr[9];

bit_out[7]=lfsr[15]^lfsr[12]^lfsr[11]^lfsr[10];

bit_out[8]=lfsr[0]^lfsr[13]^lfsr[12]^lfsr[11];

bit_out[9]=lfsr[1]^lfsr[14]^lfsr[13]^lfsr[12];

bit_out[10]=lfsr[2]^lfsr[15]^lfsr[14]^lfsr[13];

bit_out[11]=lfsr[3]^lfsr[15]^lfsr[14];

bit_out[12]=lfsr[4]^lfsr[15];

bit_out[13]=lfsr[5];

bit_out[14]=lfsr[6];

bit_out[15]=lfsr[7];

lfsr_reg[15:0]=bit_out[15:0];

end

endtask

always @(posedge clk or negedge rst)

begin

if(!rst)

begin

Data_out<=8'b00000000;

lfsr<=16'hffff;

end

else

begin

Data_out<=shift_reg;

lfsr<=lfsr_reg;

end

end

always @(posedge clk)

begin

if(Data_in==8'b00111100||Data_in==8'b10111100||Data_in==8'b00011100||Data_in==8'b01011100

||Data_in==8'b01111100||Data_in==8'b10011100||Data_in==8'b11011100||Data_in==8'b11111100

||Data_in==8'b11110111||Data_in==8'b11111011||Data_in==8'b11111101||Data_in==8'b11111110)

begin

k_flag<=1;

end

else

k_flag<=0;

end

always @(*)

begin

case(Data_in)

8'b10111100: //com

begin

shift_reg=Data_in;

lfsr_reg='hffff;

end

8'b00111100: //skp

begin

shift_reg=Data_in;

lfsr_reg=lfsr;

end

8'b11111111,8'b00010111,8'b11000000,8'b00010100,8'b10110010,8'b11100111,8'b00000010,8'b10000010,

8'b01110010,8'b01101110,8'b00101000,8'b10100110,8'b10111110,8'b01101101,8'b10111111,8'b01001010,

8'b01000101,8'b00000000,8'b00000001,8'b00000100,8'b00000101,8'b00001000,8'b00001001,8'b00001100,

8'b00001101,8'b00011100,8'b01011100,8'b01111100,8'b10011100,8'b11011100,8'b11111100,8'b11110111,

8'b11111011,8'b11111101,8'b11111110: //TSEQ/K_code

begin

shift_reg=Data_in;

lfsr_shift;

end

default: begin

raoma;

lfsr_shift;

end

endcase

end

endmodule

求大神指导

module Data_SCRAM_tb;

wire [7:0] Data_out;

wire k_flag;

reg[7:0] Data_in;

reg clk,rst;

initial

begin

clk=0;

rst=0;

#2 rst=1;

#1000

$stop();

end

always #10 clk=~clk;

always @(posedge clk or negedge rst)

begin

if(!rst)

Data_in<=8'b00000000;

else

Data_in<=Data_in+8'b00000001;

end

Data_SCRAM Dtest(.Data_in(Data_in),.Data_out(Data_out),.clk(clk),.rst(rst),.k_flag(k_flag));

endmodule

module Data_SCRAM(Data_in,Data_out,clk,rst,k_flag); //程序源码

input clk,rst;

input [7:0] Data_in;

output k_flag;

output [7:0] Data_out;

reg k_flag;

reg [7:0]Data_out;

reg [7:0] shift_reg;

reg [15:0] lfsr;

reg[7:0] scrambit;

reg[15:0] bit_out;

reg[15:0] lfsr_reg;

integer i;

task raoma;

begin

for(i=0;i<8;i=i+1) begin

scrambit[i]=Data_in[i]^lfsr[15-i];end

shift_reg[7:0]=scrambit[7:0];

end

endtask

task lfsr_shift;

begin

bit_out[0]=lfsr[8];

bit_out[1]=lfsr[9];

bit_out[2]=lfsr[10];

bit_out[3]=lfsr[11]^lfsr[8];

bit_out[4]=lfsr[12]^lfsr[9]^lfsr[8];

bit_out[5]=lfsr[13]^lfsr[10]^lfsr[9]^lfsr[8];

bit_out[6]=lfsr[14]^lfsr[11]^lfsr[10]^lfsr[9];

bit_out[7]=lfsr[15]^lfsr[12]^lfsr[11]^lfsr[10];

bit_out[8]=lfsr[0]^lfsr[13]^lfsr[12]^lfsr[11];

bit_out[9]=lfsr[1]^lfsr[14]^lfsr[13]^lfsr[12];

bit_out[10]=lfsr[2]^lfsr[15]^lfsr[14]^lfsr[13];

bit_out[11]=lfsr[3]^lfsr[15]^lfsr[14];

bit_out[12]=lfsr[4]^lfsr[15];

bit_out[13]=lfsr[5];

bit_out[14]=lfsr[6];

bit_out[15]=lfsr[7];

lfsr_reg[15:0]=bit_out[15:0];

end

endtask

always @(posedge clk or negedge rst)

begin

if(!rst)

begin

Data_out<=8'b00000000;

lfsr<=16'hffff;

end

else

begin

Data_out<=shift_reg;

lfsr<=lfsr_reg;

end

end

always @(posedge clk)

begin

if(Data_in==8'b00111100||Data_in==8'b10111100||Data_in==8'b00011100||Data_in==8'b01011100

||Data_in==8'b01111100||Data_in==8'b10011100||Data_in==8'b11011100||Data_in==8'b11111100

||Data_in==8'b11110111||Data_in==8'b11111011||Data_in==8'b11111101||Data_in==8'b11111110)

begin

k_flag<=1;

end

else

k_flag<=0;

end

always @(*)

begin

case(Data_in)

8'b10111100: //com

begin

shift_reg=Data_in;

lfsr_reg='hffff;

end

8'b00111100: //skp

begin

shift_reg=Data_in;

lfsr_reg=lfsr;

end

8'b11111111,8'b00010111,8'b11000000,8'b00010100,8'b10110010,8'b11100111,8'b00000010,8'b10000010,

8'b01110010,8'b01101110,8'b00101000,8'b10100110,8'b10111110,8'b01101101,8'b10111111,8'b01001010,

8'b01000101,8'b00000000,8'b00000001,8'b00000100,8'b00000101,8'b00001000,8'b00001001,8'b00001100,

8'b00001101,8'b00011100,8'b01011100,8'b01111100,8'b10011100,8'b11011100,8'b11111100,8'b11110111,

8'b11111011,8'b11111101,8'b11111110: //TSEQ/K_code

begin

shift_reg=Data_in;

lfsr_shift;

end

default: begin

raoma;

lfsr_shift;

end

endcase

end

endmodule

求大神指导

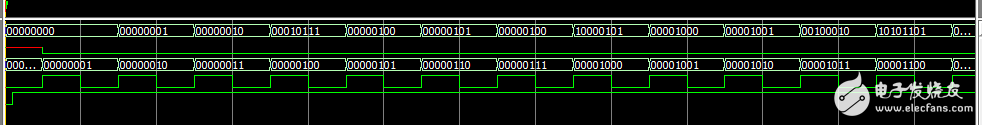

功能仿真

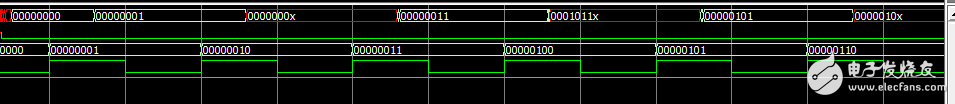

时序仿真

学习学习…………