FPGA实战演练逻辑篇3:FPGA与CPLD

时间:10-02

整理:3721RD

点击:

FPGA与CPLD(特权同学版权所有)

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

尽管很多人听说过FPGA和CPLD,但是关于FPGA与CPLD之间的区别,了解的人可能不是很多。虽然FPGA与CPLD都是“可反复编程的逻辑器件”,但是在技术上却有一些差异。简单地说,FPGA就是将CPLD的电路规模、功能、性能等方面强化之后的产物。(特权同学版权所有)

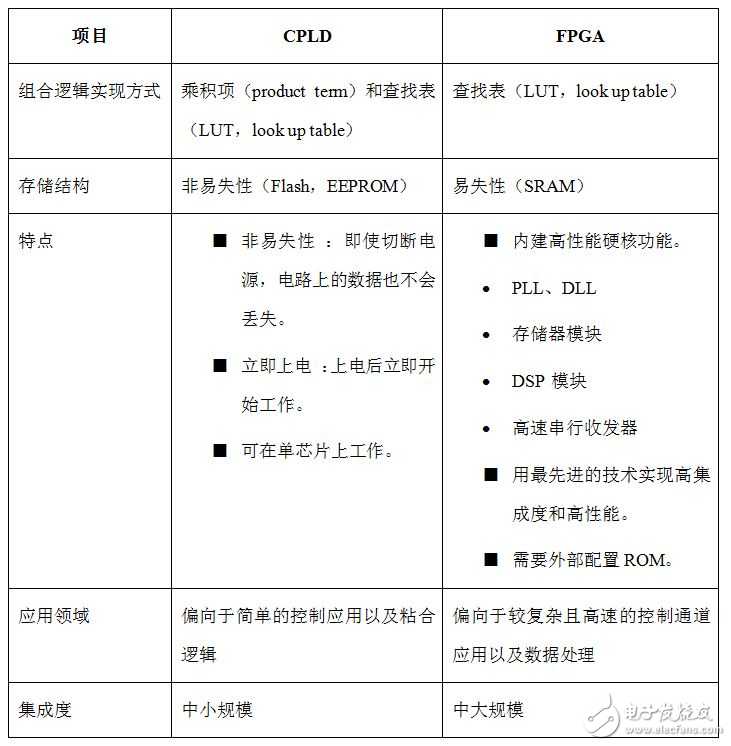

一般而言, FPGA与CPLD之间的区别如表1.1所示。(特权同学版权所有)

表1.1 FPGA和CPLD的比较

总而言之,FPGA和CPLD最大的区别是他们的存储结构不一样,这同时也决定了他们的规模不一样。但是从使用和实现的角度来看,其实他们所使用的语言以及开发流程的各个步骤几乎是一致的。对于大多数的初学者来说,学FPGA还是CPLD都是没问题的,只要掌握好他们的开发设计流程,你会发现甚至他们的应用方法和技巧都是相通的。对于大都数的电子工程师来说,将来不一定都有机会用FPGA做一些高性能的产品,但是用颗小小的CPLD来实现一些辅助开发倒是很有可能的。(特权同学版权所有)