用quartusII编程3-8译码器,时序仿真出错,类似延迟,求指教

时间:10-02

整理:3721RD

点击:

代码如下:

// decoder 3 to 8 decoder with an enable control;

module decoder ( y , en , a );

output [ 7:0 ] y; // 八位输出

input en; // 使能端

input [ 2:0 ] a; // 三位地址端

reg [ 7:0 ] y;

always @ ( en or a )

if ( en )

case ( a )

3'b000 : y = 8'b1111_1110;

3'b001 : y = 8'b1111_1101;

3'b010 : y = 8'b1111_1011;

3'b011 : y = 8'b1111_0111;

3'b100 : y = 8'b1110_1111;

3'b101 : y = 8'b1101_1111;

3'b110 : y = 8'b1011_1111;

3'b111 : y = 8'b0111_1111;

default : y = 8'b1111_1111;

endcase

else

y = 8'b1111_1111;

endmodule // end of decoder;

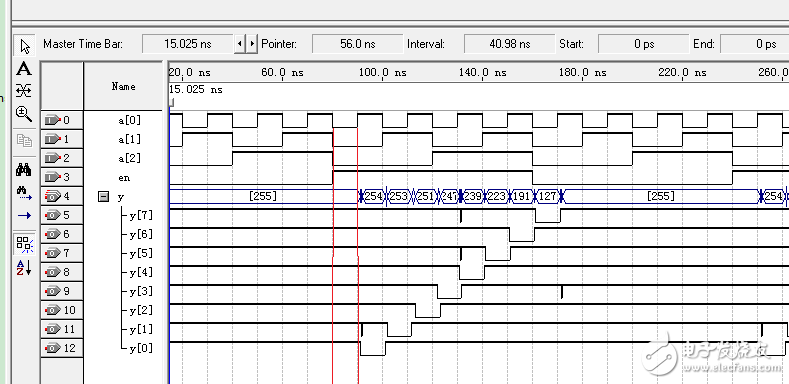

产生的波形文件见下图。

本来应该是,en=1,a=000的时候,输出y=1111_1110;结果y=1111_1110却跑到a=001的时候去了。

本人小白,刚学verilog hdl,写一个3-8译码器就出错了,还望各位大哥大姐多多指教!

// decoder 3 to 8 decoder with an enable control;

module decoder ( y , en , a );

output [ 7:0 ] y; // 八位输出

input en; // 使能端

input [ 2:0 ] a; // 三位地址端

reg [ 7:0 ] y;

always @ ( en or a )

if ( en )

case ( a )

3'b000 : y = 8'b1111_1110;

3'b001 : y = 8'b1111_1101;

3'b010 : y = 8'b1111_1011;

3'b011 : y = 8'b1111_0111;

3'b100 : y = 8'b1110_1111;

3'b101 : y = 8'b1101_1111;

3'b110 : y = 8'b1011_1111;

3'b111 : y = 8'b0111_1111;

default : y = 8'b1111_1111;

endcase

else

y = 8'b1111_1111;

endmodule // end of decoder;

产生的波形文件见下图。

本来应该是,en=1,a=000的时候,输出y=1111_1110;结果y=1111_1110却跑到a=001的时候去了。

本人小白,刚学verilog hdl,写一个3-8译码器就出错了,还望各位大哥大姐多多指教!

结果像产生了延迟一样。

代码没什么问题吧!你看一下编译有没有什么问题!

谢谢。我再看看吧。

程序和仿真都没有问题,你的输出用了寄存器,所以y会在下一个时钟沿到来时输出,就像延迟一个时钟一样

感谢回复。但是我依然不太明白:我用的是电平触发,“always @(en or a)”,并不是时序电路啊,好像没有用到触发器吧,怎么会是因为触发器产生的延时呢?还望指明,谢谢啦!

输出端Y设置了一个reg,寄存器,输出会存放在这里一个时钟周期,下个时钟周期输出,我感觉是这样,你看看RTL图

谢谢耐心回复。我查了一下设计的RTL图(见《3_8译码器的RTL图》),结合自己把输出y声明为reg类型,确实造成了输出延时。这和always块使用组合逻辑,还是时序逻辑无关。再次感谢您的耐心回复。

3_8译码器的RTL图