哪位朋友看看 扫描数码管 的问题 思考好久了还是想不通

时间:10-02

整理:3721RD

点击:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cymometer is

port ( sysclk : in std_logic; --10MHZ频率输入

clkin : in std_logic; --待测频率信号输入

seg7:out std_logic_vector(6 downto 0); --7段显示控制信号(abcdefg)

scan:out std_logic_vector(7 downto 0)); --数码管地址选择信号

end;

architecture one of cymometer is

signal cnt:std_logic_vector (24 downto 0);

signal clk_cnt:std_logic;

signal cntp1,cntp2,cntp3,cntp4,cntp5,cntp6,cntp7,cntp8:std_logic_vector (3 downto 0);

signal cntq1,cntq2,cntq3,cntq4,cntq5,cntq6,cntq7,cntq8:std_logic_vector (3 downto 0);

signal dat:std_logic_vector(3 downto 0);

begin

-------------0.5HZ分频--------------------------

process (sysclk)

begin

if sysclk'event and sysclk='1' then

if cnt=19999999 then clk_cnt '0');

else cnt scan scan scan scan scan scan scan scan null;

end case;

end process;

process(dat)

begin

case dat is

when "0000" =>seg7 seg7 seg7 seg7 seg7 seg7 seg7 seg7 seg7 seg7 null;

end case;

end process;

end ;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cymometer is

port ( sysclk : in std_logic; --10MHZ频率输入

clkin : in std_logic; --待测频率信号输入

seg7:out std_logic_vector(6 downto 0); --7段显示控制信号(abcdefg)

scan:out std_logic_vector(7 downto 0)); --数码管地址选择信号

end;

architecture one of cymometer is

signal cnt:std_logic_vector (24 downto 0);

signal clk_cnt:std_logic;

signal cntp1,cntp2,cntp3,cntp4,cntp5,cntp6,cntp7,cntp8:std_logic_vector (3 downto 0);

signal cntq1,cntq2,cntq3,cntq4,cntq5,cntq6,cntq7,cntq8:std_logic_vector (3 downto 0);

signal dat:std_logic_vector(3 downto 0);

begin

-------------0.5HZ分频--------------------------

process (sysclk)

begin

if sysclk'event and sysclk='1' then

if cnt=19999999 then clk_cnt '0');

else cnt scan scan scan scan scan scan scan scan null;

end case;

end process;

process(dat)

begin

case dat is

when "0000" =>seg7 seg7 seg7 seg7 seg7 seg7 seg7 seg7 seg7 seg7 null;

end case;

end process;

end ;

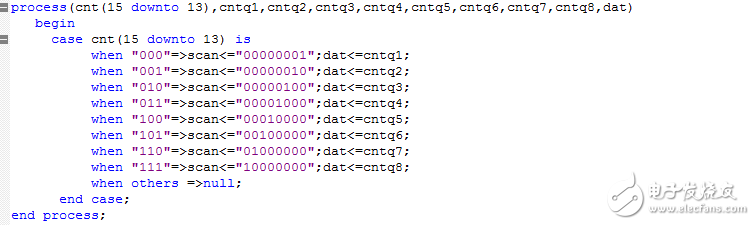

为什么是 15 downtown 13 有什么内涵没有

scan:out std_logic_vector(7 downto 0)是数码管地址控制信号

意思是不是用 7个二进制数来控制 FPGA上面的 7个数码管的使能端 ?

好迷茫啊

不是移位吧

3个二进制构成8个状态

我就是不明白为什么从15到13 为什么不是24到22 或则其他