FPGA设计实例--基于FPGA的FIR滤波器

时间:10-02

整理:3721RD

点击:

方案一:QuartusII中的IP核。但是FIR IP没有破解,放弃。

方案二:用纯硬件描述语言搭建。

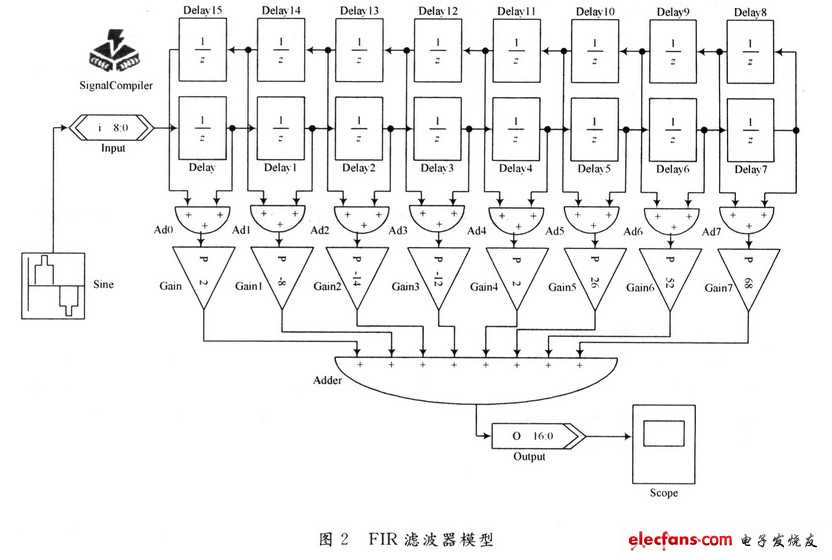

基本上分为MAC(乘积累加结构)和DA(分布式结构)。

MAC中具体结构有:

直接型FIR滤波器结构。利用FIR系数对称性特点,先对相应值相加,再做乘积运算,最后累加。该进措施可以是加上流水线结构。

实例:(参考自《EDA技术与Verilog设计》王金明编著)8KHZ采样率,8Bit输入,8Bit输出,11阶低通滤波器,fL=3.4KHZ。利用MATLAB得到滤波器系数,采用SD编码。Tips:SD(signed digit numbers有符号数字量),通过SD编码可以降低非零元素的数量。SD编码数字值域{1,0,-1},-1用1上面加“-”表示。

代码如下:

- module Fir02

- (

- input clk,

- input [7:0] x,

- output reg [15:0] y

- );

-

- reg [7:0] tap0,tap1,tap2,tap3,tap4,tap5,tap6,tap7,tap8,tap9,tap10;

- reg [7:0] t0,t1,t2,t3,t4,t5;

- reg [15:0] sum;

-

- always @(posedge clk)

- begin

- t0<=tap5;

- t1<=tap4+tap6;

- t2<=tap3+tap7;

- t3<=tap2+tap8;

- t4<=tap1+tap9;

- t5<=tap0+tap10;

-

- sum<= (t1<<4)

- +{t1[7],t1[7:1]}

- +{t1[7],t1[7],t1[7:2]}

- +{t1[7],t1[7],t1[7],t1[7:3]}

-

- -(t2<<3)

- -(t2<<2)

- +t2

- -{t2[7],t2[7],t2[7:2]}

-

- +(t3<<2)

- +t3

- +{t3[7],t3[7],t3[7:2]}

- +{t3[7],t3[7],t3[7],t3[7],t3[7:4]}

- +{t3[7],t3[7],t3[7],t3[7],t3[7],t3[7:5]}

-

- -t4

- -{t4[7],t4[7:1]}

- -{t4[7],t4[7],t4[7],t4[7:3]}

-

- +{t5[7],t5[7:1]}

- -{t5[7],t5[7],t5[7],t5[7],t5[7],t5[7:5]}

-

- +(t0<<7)

- -((t0<<2)<<2)

- -(t0<<2)

- +{t0[7],t0[7:1]}

- +{t0[7],t0[7],t0[7:2]}

- +{t0[7],t0[7],t0[7],t0[7],t0[7:4]};

-

- tap10<=tap9;

- tap9<=tap8;

- tap8<=tap7;

- tap7<=tap6;

- tap6<=tap5;

- tap5<=tap4;

- tap4<=tap3;

- tap3<=tap2;

- tap2<=tap1;

- tap1<=tap0;

- tap0<=x;

-

- y<={sum[15],sum[15],sum[15],sum[15],sum[15],sum[15],sum[15],sum[15:7]};

- end

-

- endmodule

很不错

已经下载,存档,慢慢看!谢谢

没太看懂!求解释

学习中~~

慢慢看看……

不错

dddddddddddddddddddddddddd

这个有难度, 分享简单一点的就最好啦!

谢谢分享

感谢小编的无私奉献

不错

谢谢分享!

不错,正找呢!

不错,不过代码虽简单,但是没有讲什么滤波器原理。不过对于通信类专业同学来说,基本上应该是知道的。

l请问你有用全串行DA算法做过FIR,求交流!

不错,可惜我没有学

谢谢

好东西

真心需要

好东东

谢谢大神。

xuexi

调试的效果怎么样呢?

学习!

小编无私!

;=这个符号和<=这两个运算符有啥区别?求高手解答

我把那个代码编译了一下,不成功啊,小编求解。

感谢小编的分享

学习学习,小编有做过FPGA自适应滤波器的实现吗,求共享啊

好东西,谢谢分享

这代码怎么全是语法错误,小编出来解释下

好,顺便赚个积分

不错,可惜我没有学

复制下来了,谢谢小编吧

谢谢分享~

正在学习中,不知道什么时候能做个这个出来。

不错不错不错不错

dddddddddddddddddddddddddddddddddddd

代码是不是有问题?里面的lt是什么变量?