ISE14.7 仿真简单的电路出错,求大家帮忙看看

时间:10-02

整理:3721RD

点击:

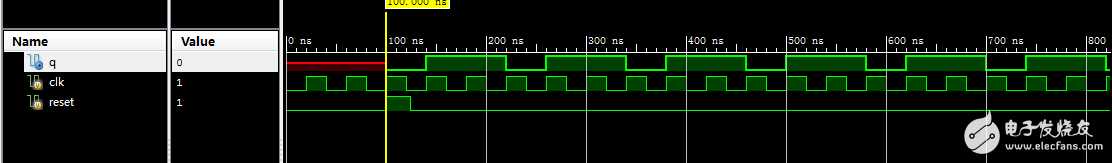

刚装几天ISE,利用自带的Isim仿真,尝试过很多教程的例子,依然是仿真出错,波形图中显示输入的变量全为高阻,输出变量当然就没有值全为红线~~

比如一个3分频的例子:

module fenpin_top(clk,reset,q);

input clk;

input reset;

output q;

reg q;

reg [1:0] count; // 设了一个2位的计数器可以从00计数到11;

always @ (posedge clk or posedge reset) // 同步复位,上升沿有效

if (reset) // 复位

begin

q<=1'b0;

count<=2'b00;

end

else if(count==0) // 第一个CLK上升沿来的时候q翻转一次计数器加一;

begin

q<=~q;

count<=count+1'b1;

end

else if(count==2) //第3个CLK上升沿来的时候输出q翻转一次计数器归零;

begin

q<=~q;

count<=2'b00;

end

else // 第二个CLK上升沿来的时候q不动作,计数器加一。

begin

count<=count+1'b1;

end

endmodule

testbench如下:

module tb_fenpin_top;

// Inputs

reg clk;

reg reset;

// Outputs

wire q;

// Instantiate the Unit Under Test (UUT)

fenpin_top uut (

.clk(clk),

.reset(reset),

.q(q)

);

initial

begin

// Initialize Inputs

clk = 1'b0;

reset = 1'b0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

clk=1'b0;

reset=1'b1;

#24 reset =1'b0;

end

always

#20 clk=~clk;

endmodule

不知道是否软件设置问题,ISE14.7版本的

FPGA入门中,希望大家帮忙看看,无限感激

如果你仿真结果出不来的话 是不是仿真时间太短了

我能问你个问题么:

你这个用的相应的芯片和板子是哪种的 可否给我参考下 我想去买!

file:///C:\Users\zpw546\AppData\Roaming\Tencent\Users\969921328\QQ\WinTemp\RichOle\`A0]PW~YS4_]HX5]O1Y{)L4.jpg

比如一个3分频的例子:

module fenpin_top(clk,reset,q);

input clk;

input reset;

output q;

reg q;

reg [1:0] count; // 设了一个2位的计数器可以从00计数到11;

always @ (posedge clk or posedge reset) // 同步复位,上升沿有效

if (reset) // 复位

begin

q<=1'b0;

count<=2'b00;

end

else if(count==0) // 第一个CLK上升沿来的时候q翻转一次计数器加一;

begin

q<=~q;

count<=count+1'b1;

end

else if(count==2) //第3个CLK上升沿来的时候输出q翻转一次计数器归零;

begin

q<=~q;

count<=2'b00;

end

else // 第二个CLK上升沿来的时候q不动作,计数器加一。

begin

count<=count+1'b1;

end

endmodule

testbench如下:

module tb_fenpin_top;

// Inputs

reg clk;

reg reset;

// Outputs

wire q;

// Instantiate the Unit Under Test (UUT)

fenpin_top uut (

.clk(clk),

.reset(reset),

.q(q)

);

initial

begin

// Initialize Inputs

clk = 1'b0;

reset = 1'b0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

clk=1'b0;

reset=1'b1;

#24 reset =1'b0;

end

always

#20 clk=~clk;

endmodule

不知道是否软件设置问题,ISE14.7版本的

FPGA入门中,希望大家帮忙看看,无限感激

代码是正确的,应该是软件设置的问题。

继续求教,之前在论坛看到一种说法是,ISE14.2之后的版本,顶层文件都得自己手输入,写代码时设的顶层模块和测试文件不同,不太懂什么意思...写verilog的代码也有一段时间了,之前都是综合通过就算,谁知一做时序仿真就卡住了

我没装你使用的软件,我用altera-modelsim仿了你的代码,可以看到波形的,没有问题。如果如你说的,应该是你没有指定testbench。

没有指定testbench的意思是?

因为实验室的FPGA板子都是xilinx的,所以就配套用ISE了。

试过很多感觉应该没错的代码,波形仿真就没成功过,一直在郁闷

我不知道你问题解决没我也是用的ise14.7 用你这个代码仿真出来应该是对的 你看哈

如果你仿真结果出不来的话 是不是仿真时间太短了

我能问你个问题么:

你这个用的相应的芯片和板子是哪种的 可否给我参考下 我想去买!

file:///C:\Users\zpw546\AppData\Roaming\Tencent\Users\969921328\QQ\WinTemp\RichOle\`A0]PW~YS4_]HX5]O1Y{)L4.jpg

我现在也遇到这样的问题了,我用的是ise14.7~~你找到解决办法了么?

是不是仿真的时候选错文件了,应该选择testbench那个文件进行仿真

我也是14.7,我也是这个问题,不明白该怎么做,求解决方法啊!