ISE用Modelsim SE仿真出错,请大家帮忙看看

下面是Transcript中的最后几行,大家看看这显示什么问题,谢谢了!

# Top level modules:

# glbl

# vsim -L xilinxcorelib_ver -L unisims_ver -L unimacro_ver -lib work -voptargs=\"+acc\" -t 1ps work.top glbl

# ** Note: (vsim-3812) Design is being optimized...

#

# Loading work.top(fast)

# Loading work.glbl(fast)

# .main_pane.wave.interior.cs.body.pw.wf

# .main_pane.structure.interior.cs.body.struct

# .main_pane.objects.interior.cs.body.tree

VSIM2>

Transcript

是不是没初始化赋值啊? 所以不能判断状态就都高阻了? 建议你重新检查下测试文本

我代码是个分频,以前做的在Quarts II上用Modelsim Altera仿真没问题,仿真文件应该没问题

建议你把测试文件和代码贴一下 Transcript是没问题的

这是测试文本

module test;

// Inputs

reg clk;

reg reset;

// Outputs

wire clk11;

top uut (

.clk(clk),

.reset(reset),

.clk11(clk11)

);

initial begin

clk=1'b1;

forever

#25

clk=~clk;

end

initial begin

reset=1'b0;

#50

reset=1'b1;

end

endmodule

两个……initial……

initial begin

clk=1'b1;

reset=1'b0;

#50

reset=1'b1;

end

always #25 clk=~clk;

你改成这样试试?

还是高阻。应该不是测试文本的问题,我在Quartus上用过,编译没错仿真也能出正确波形。

现在我怀疑是不是软件设置的问题,毕竟是刚上手

也有可能…… 找个范例看看吧……

总觉得好像就没有运行起来的样子 是不是没设置执行时间?

这是代码,11分频,占空比不是50%

`timescale 1ns / 1ps

module test (clk,reset,clk11);

input clk,reset;

output clk11;

reg [3:0]i;

reg clk11;

always @( posedge clk)

begin

if(!reset)

begin

i<=4'b0;

clk11<=0;

end

else if(i==4'd5)

begin

clk11<=~clk11;

i<=i+4'b1;

end

else if(i==4'd10)

begin

i<=4'b0;

clk11<=~clk11;

end

else

i<=i+4'b1;

end

endmodule

程序没啥错误……估计还是配置有问题吧 你好好看看

设了时间,1000ns

你看看Transcript 里有没有 一般有命令的应该

这是在Quartus用Modelsim Altera仿真的,我标出来的红色字体是在ISE Modelsim SE仿真时没有的,能看出是啥问题吗

# Top level modules:

# test_vlg_tst

#

# vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L cycloneii_ver -L rtl_work -L work -voptargs="+acc" test_vlg_tst

# vsim -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L cycloneii_ver -L rtl_work -L work -voptargs=\"+acc\" -t 1ps test_vlg_tst

# Loading work.test_vlg_tst

# Loading work.test

#

# add wave *

# view structure

# .main_pane.structure.interior.cs.body.struct

# view signals

# .main_pane.objects.interior.cs.body.tree

# run -all

第一个应该是针对 altera调用的 函数 没有应该是xilinx不需要吧?

第二个是表示的是一直运行仿真 直到你手动停止

run + 时间 表示仿真多长时间

谢谢你这么热心!

我刚才用他自带的Isim来仿真,也是高阻,问题在ISE,看来跟 Modelsim SE没关系。彻底崩溃了,还是用QuartusII比较方便。

我实验室用的电脑上QuartusII和ISE都能用Modelsim Altera仿真,这是一位刚毕业的师兄搭建的开发环境。后来被我一弄,ISE不能用它仿真了。

呵呵 多操作操作熟悉了就知道怎么改了~ 其实软件还是比较简单的

仿出来了,真高兴。

我的ISE是14.2的,顶层文件都得自己手输入。写代码是设的顶层模块和测试文件不同

谢谢cleusewitz的帮助,我的问题解决了,纠结了好几天。

ISE14.2不知道其他人遇到这样的问题没有,顶层模块要自己输入。

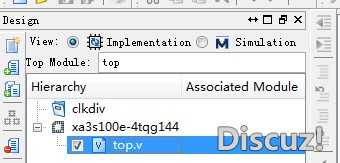

如图所示(希望对其他人有帮助)

看吧 多操作就能找到错误了~

xilinx FPGA设计必须用modelsim进行波形仿真吗,ISE不是也有波形仿真功能吗

ise有自带的仿真,我不太喜欢用,因为之前一直用modelsim。

我原来用quartusII软件仿真时,就用波形仿真器。现在刚装了ISE不长时间,还是刚接触Modelsim。还需要学习

小编求教,我的分频模块仿真还是不行,同样的问题,输入可以,输出为X态

仿真前要把测试文本(testbench)设为顶层文件

不错,下载下来看看。

我也遇到这个问题,求教怎样解决,我用的是14.7的版本

需要将testbench设为顶层?但是右键打开的菜单,set as top module 的选项无法选择,是这样设吗?

仿真就没成功过,用自带的Isim,求教小编,不胜感激...

我也是仿真不出来,输入如果用std_logic的类型就一直是高阻态,要是换成bit类型就变成输出全为0,没有变化,怎么解决呢?

你仿真的问题解决了吗?可以告诉我方法吗?我现在也遇到这样的问题

如果是其中一个模块,就添加到一个新的工程呗,编写testbench,肯定可以的!